여러가지 조합논리회로

코드변환기

- 디지털 시스템에서 시스템들이 교환할 정보에 대해 서로 다른 코드를 사용한다면 **코드 변환이 필요

- 하나의 이진코드를 다른 이진 코드로 바꾸어 주는 조합논리회로

- 다양한 코드 변환기 존제

- BCD-3 초과코드- BCD-9 보수변환기

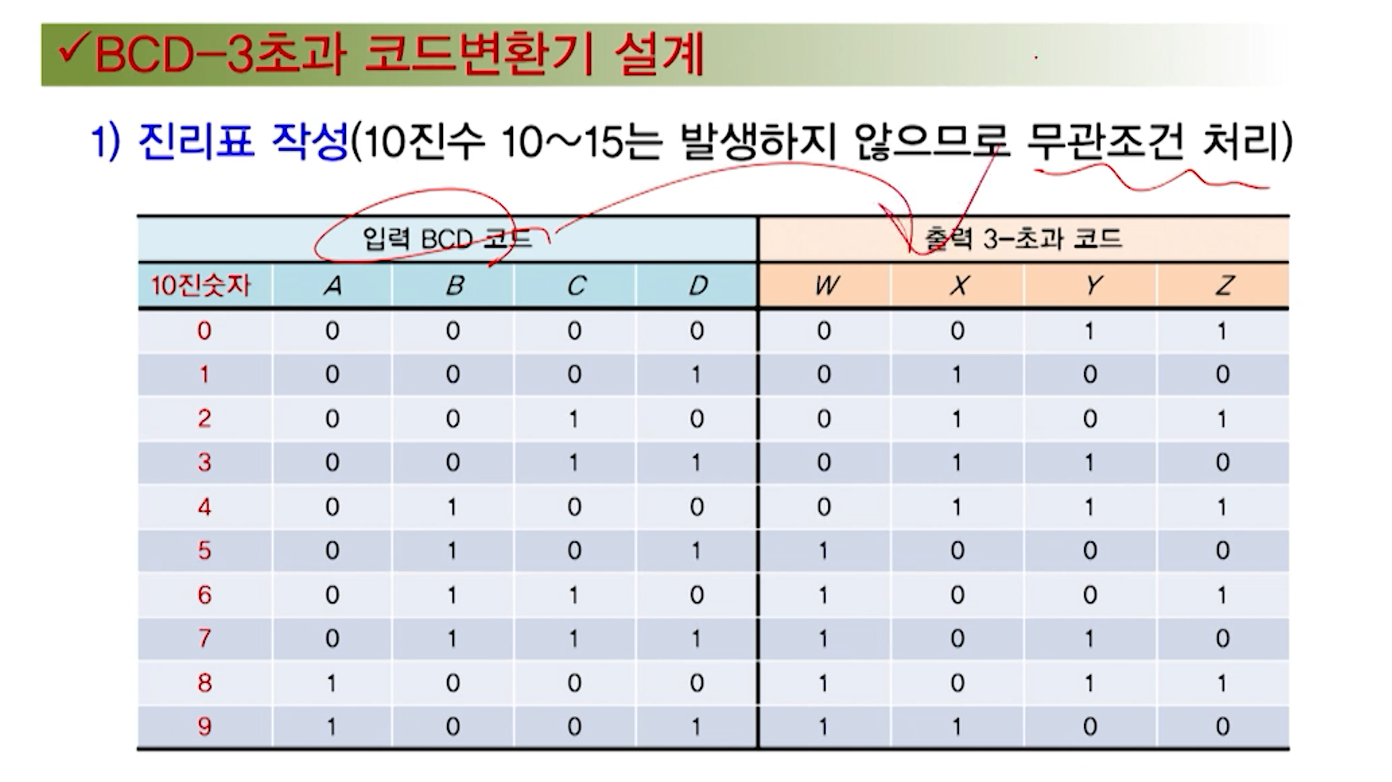

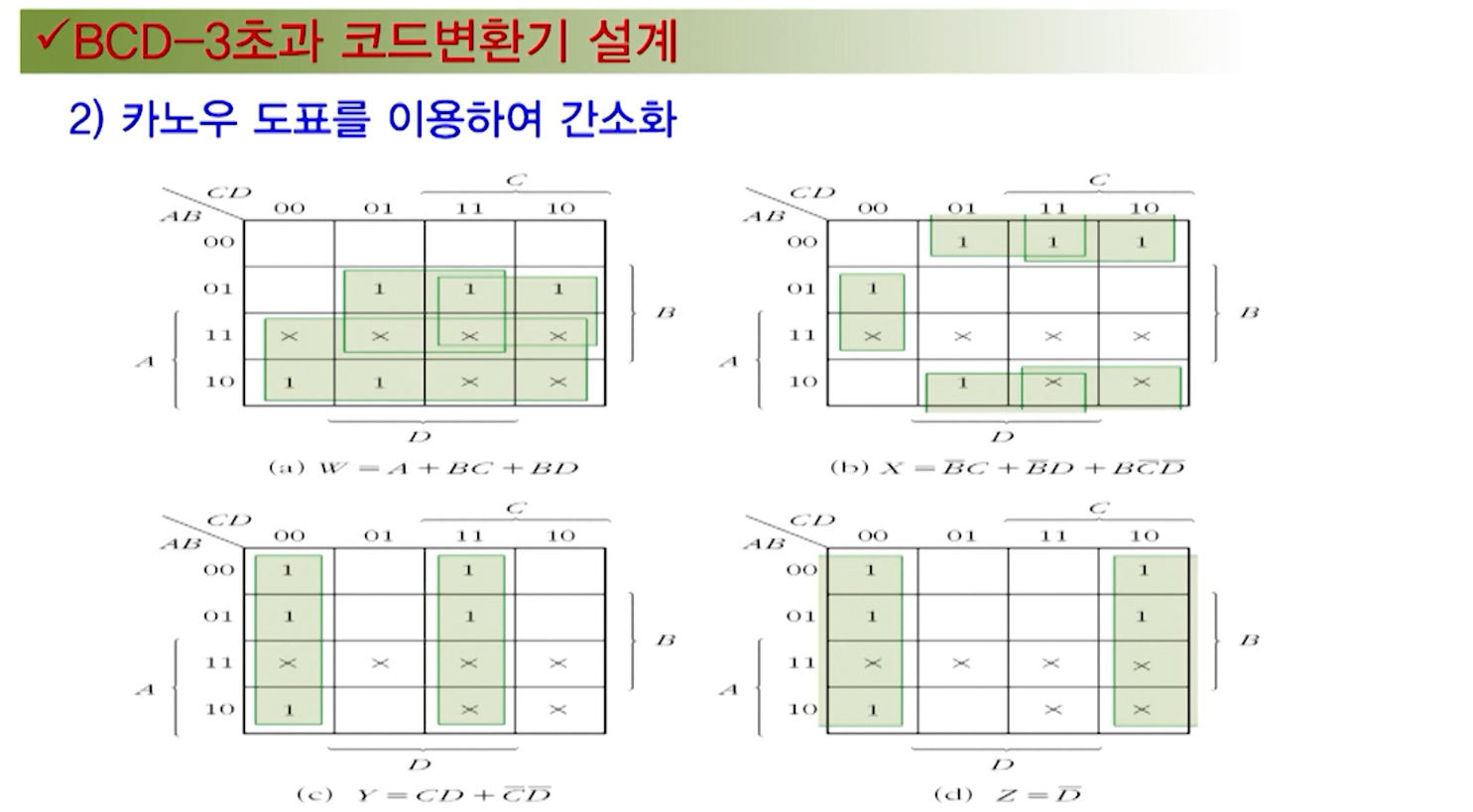

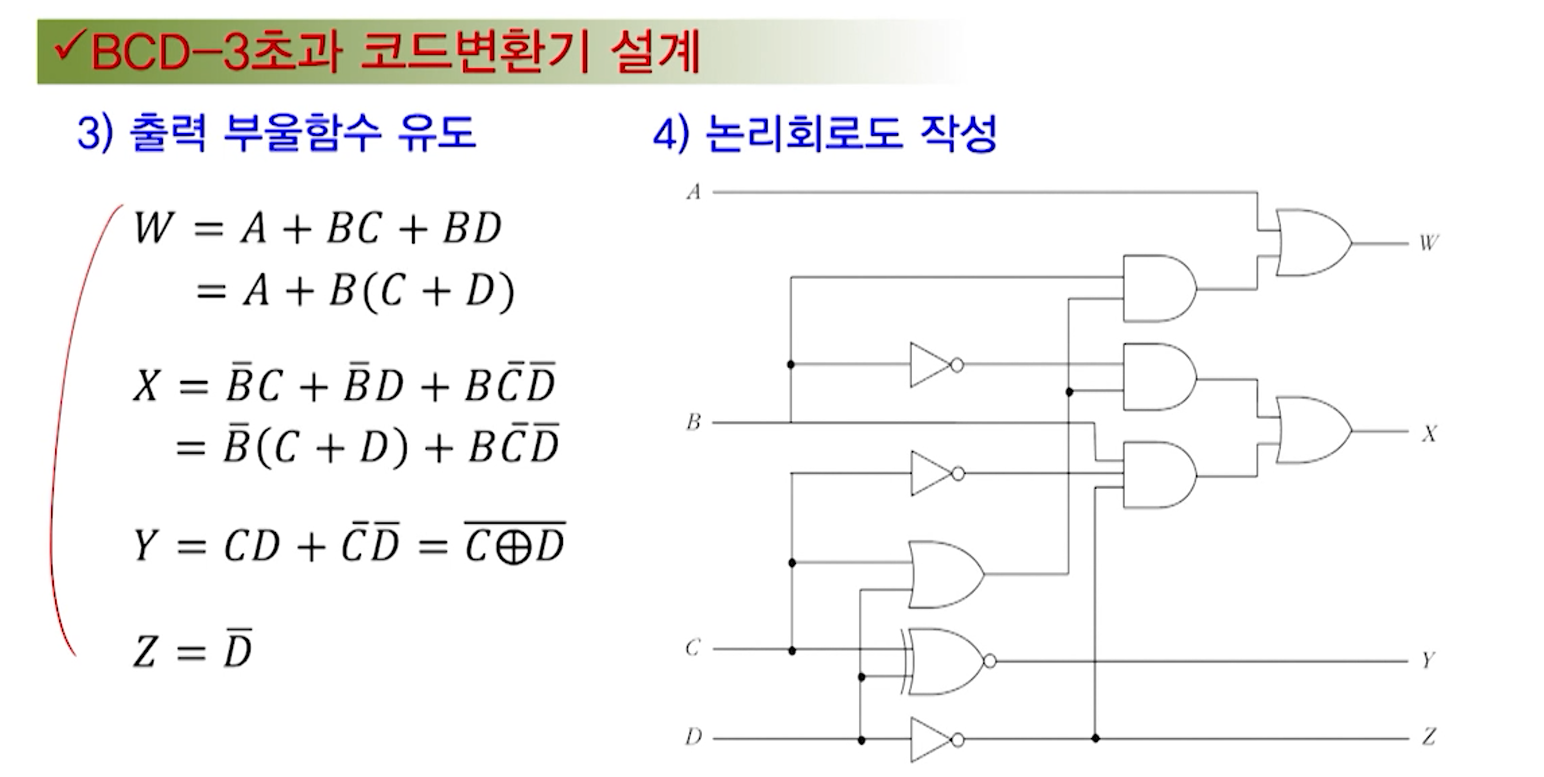

BCD-3 초과 변환기

- BCD 코드를 3-초과 코드로 바꾸는 변환기

- BCD 코드를 3-초과 코드는 4비트를 이용하여 10진수 표현

- 따라서 변환회로는 4개입력과 4개출력 팔요

- 설계과정

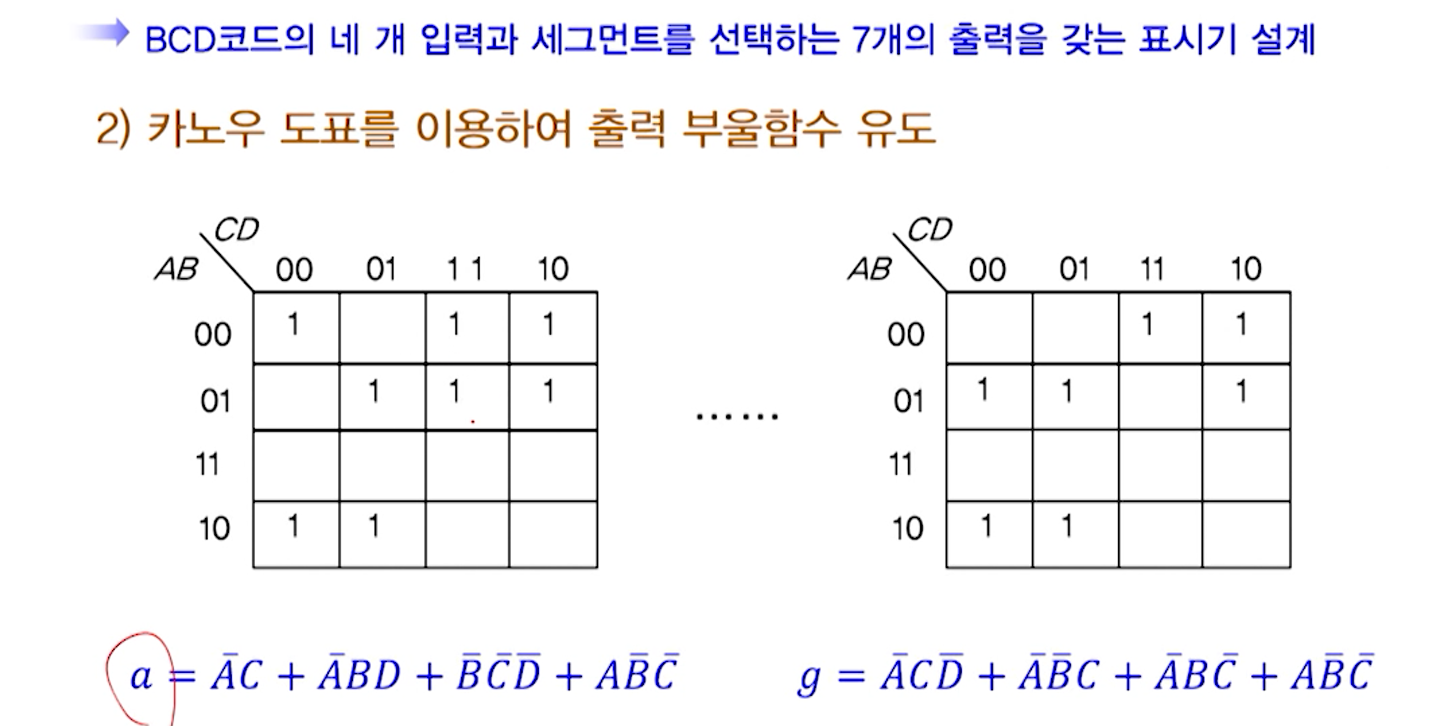

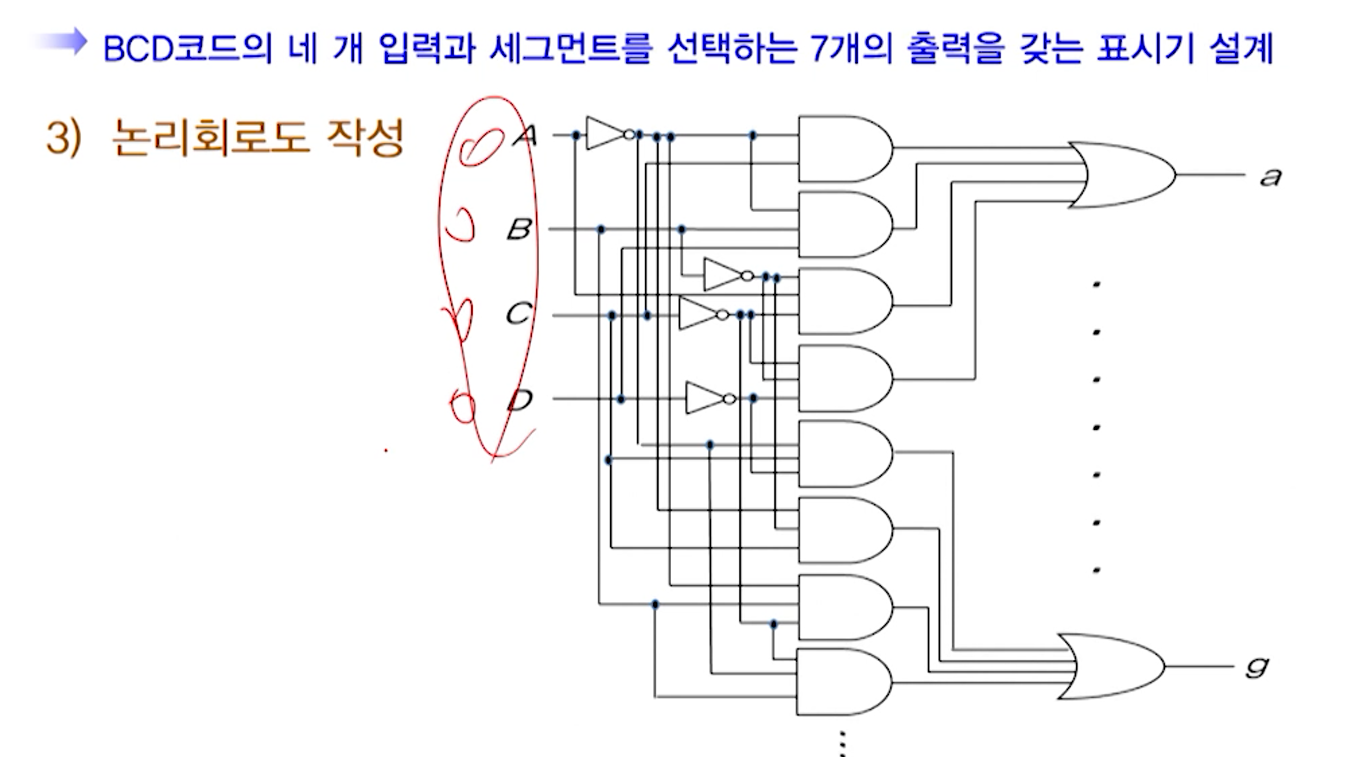

1. 진리표작성- 카르노 도표 아용 간소화(부울함수 유도)

- 출력 부울함수 유도

- 논리회로도 작성

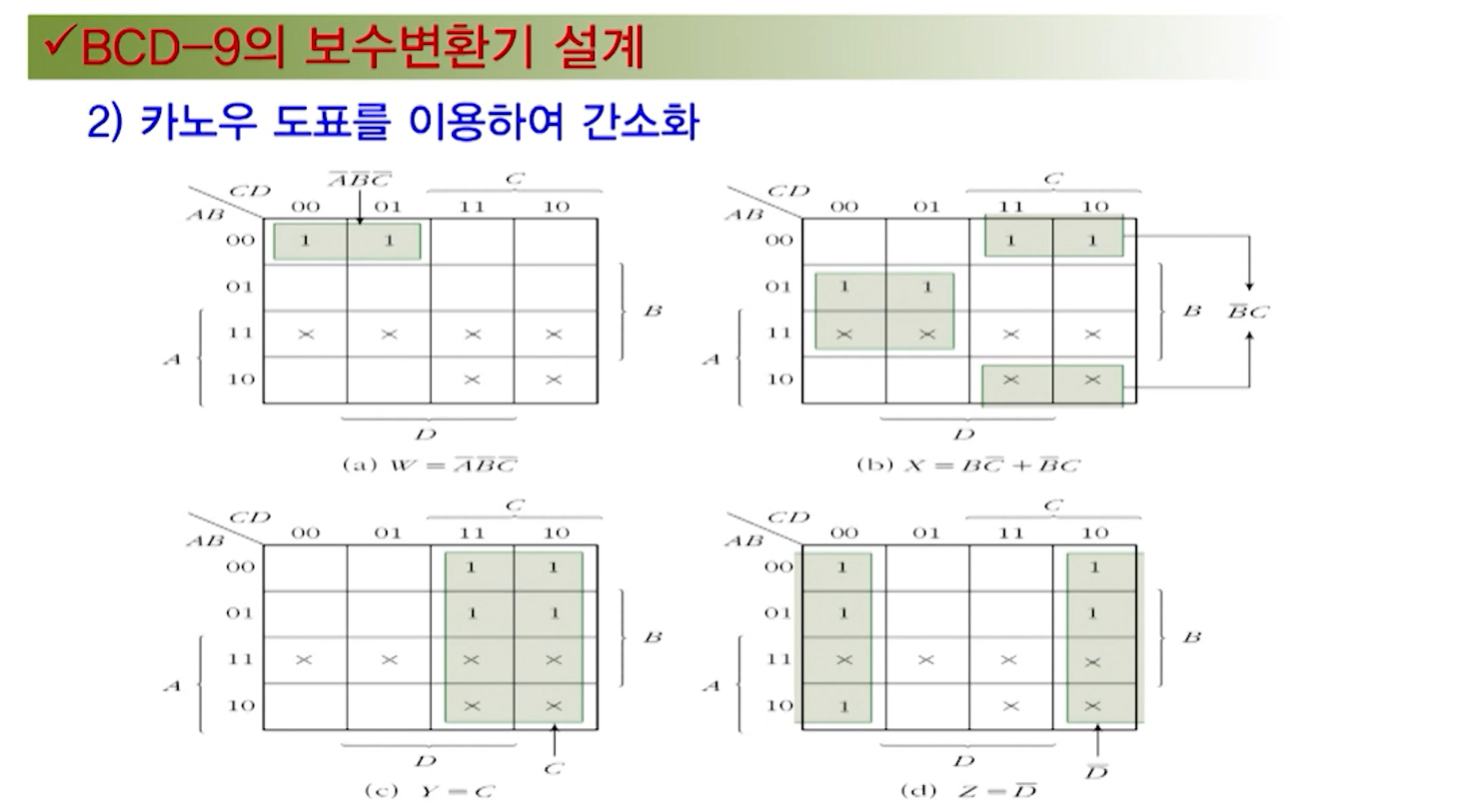

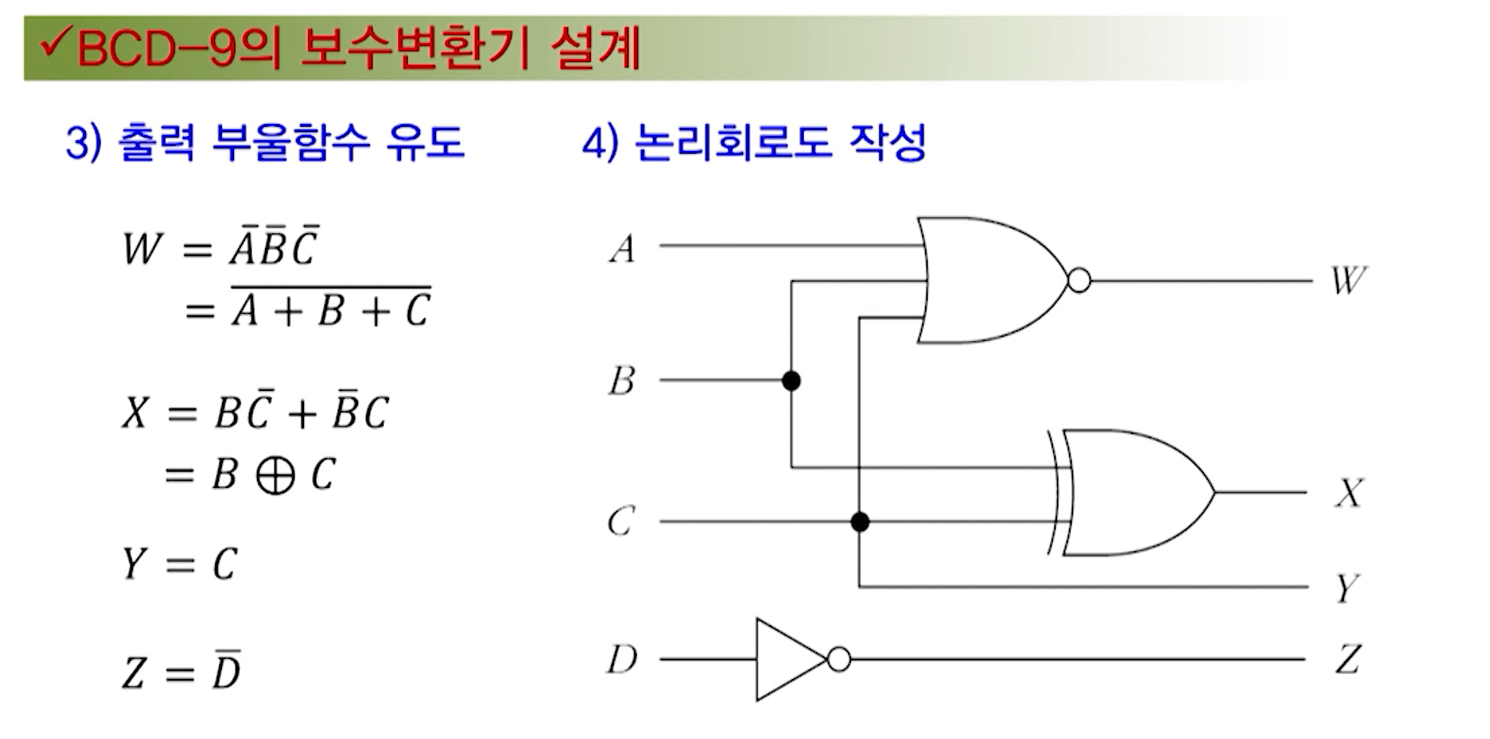

BCD-9 보수 변환기

패리티 발생기/검사기

- 디지털 시스템에서 2진 정보를 주고 받을 떄 잡음이나 회로상의 문제로 에러 발생

- 이러한 에러 검출을 위해 전송되는 정보에 에러 검출용 비트 추가해 전송

- 이때 추가되는 에러 검출용 비트 : 패리티 비트

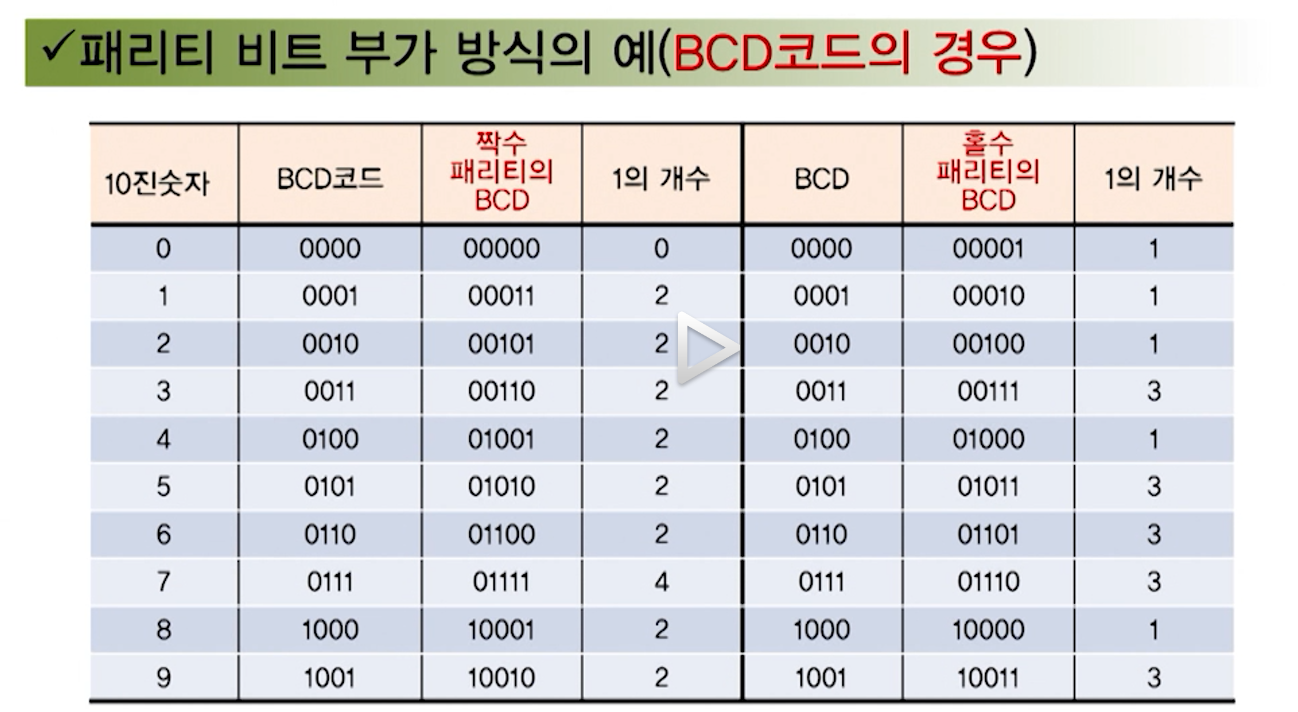

패리티 비트를 이용하는 방식

- 짝수 패리티 검출방식

- 2진 정보 속에 1의 개수가 패리티 비트를 포함하여 짝수가 되도록 패리티 비트를 부과하는 방식

- 홀수 패리티 검출방식 -> 주로 사용

- 2진 정보 속에 1의 개수가 패리티 비트를 포함하여 홀수가 되도록 패리티 비트를 부과하는 방식

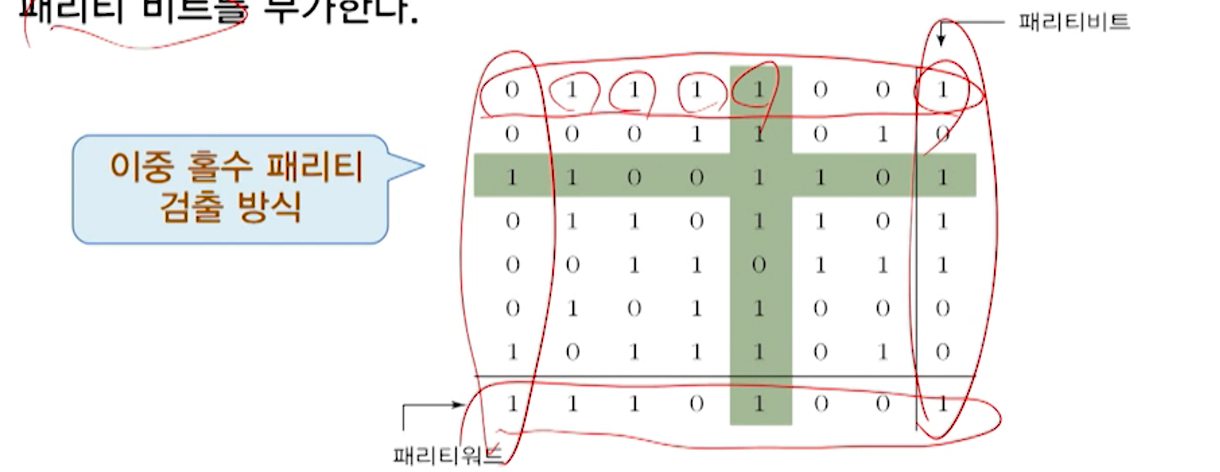

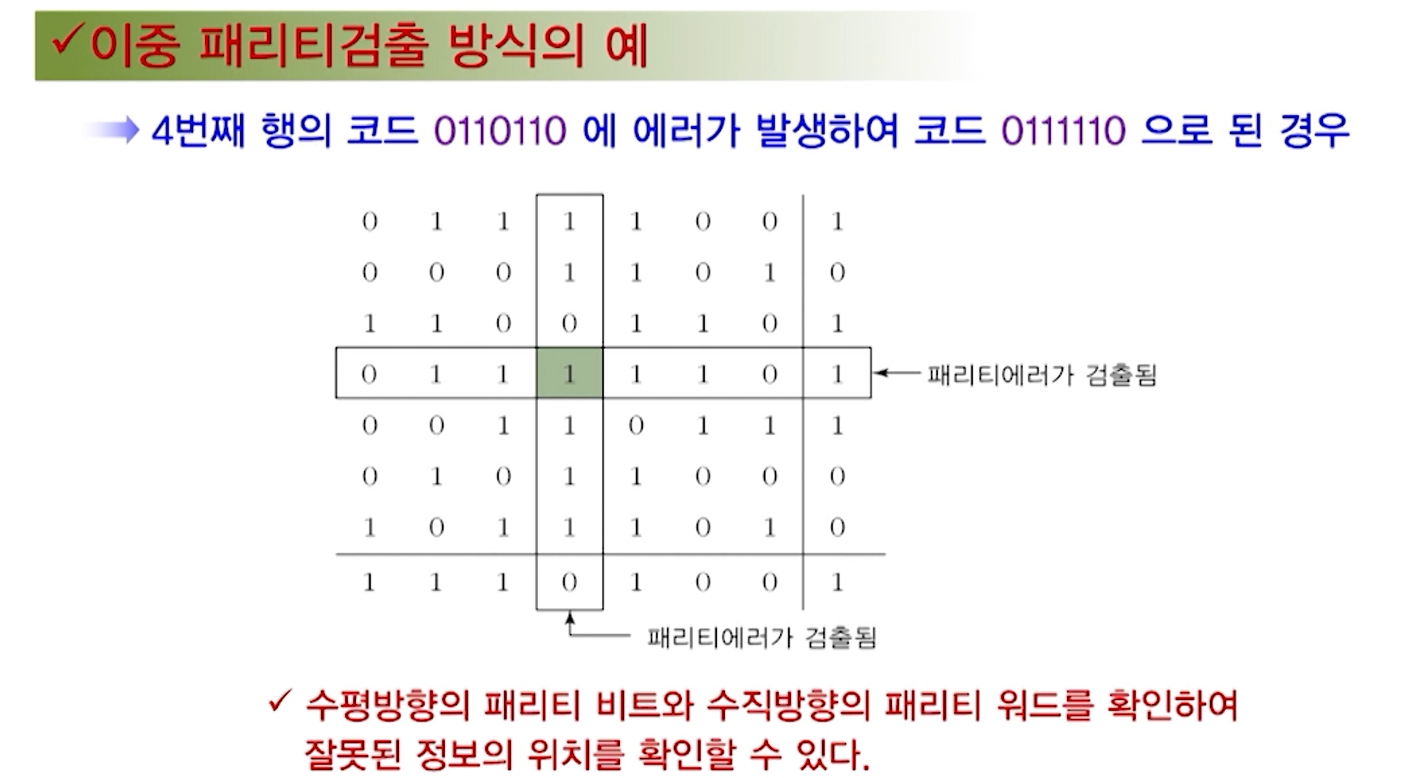

이중 패리티 검출방식

- 일반 패리티 검출방식은 1개의 에러가 있을떄 검출 가능

- 그러나 동시에 2개의 에러가 있으면 검출 불가능

- 이러한 경우에 사용되는 방법이 이중 패리티 검출방식

- 이 방식은 코드를 한 묶음으로 하여, 그 묶음의 수직방향과 수평방향으로 패리티 비트를 부가

홀수패리티인데 1이 6개임 -> 패리티 에러 검출

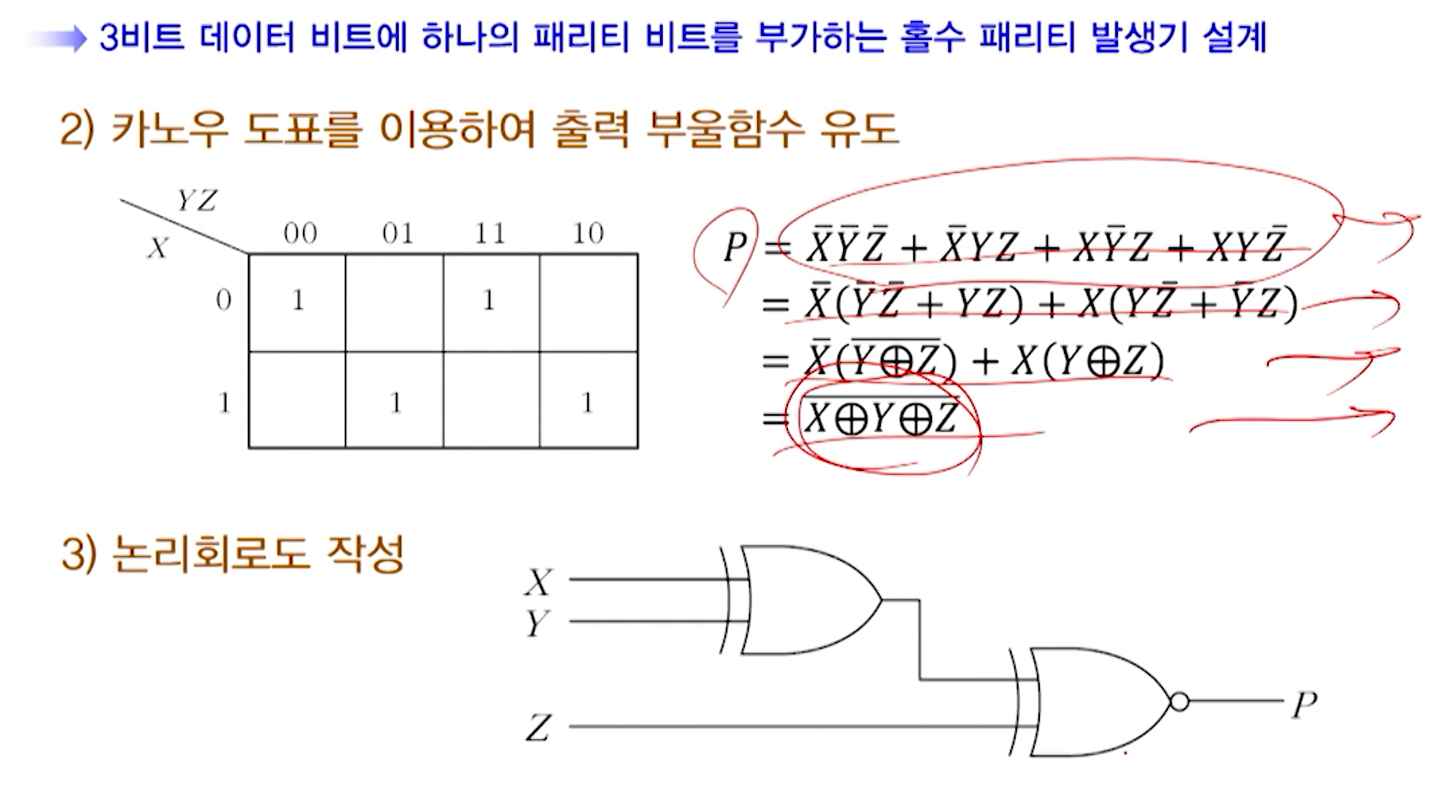

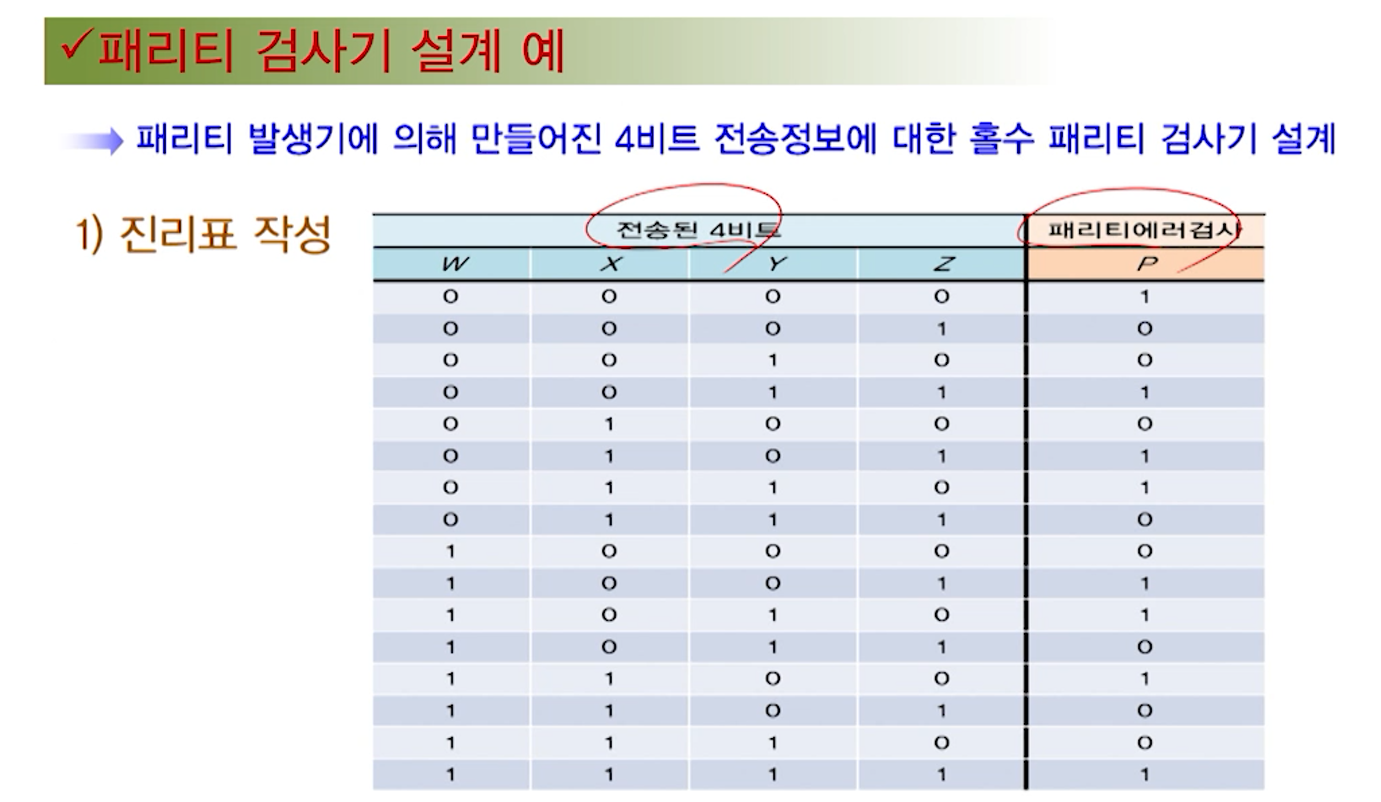

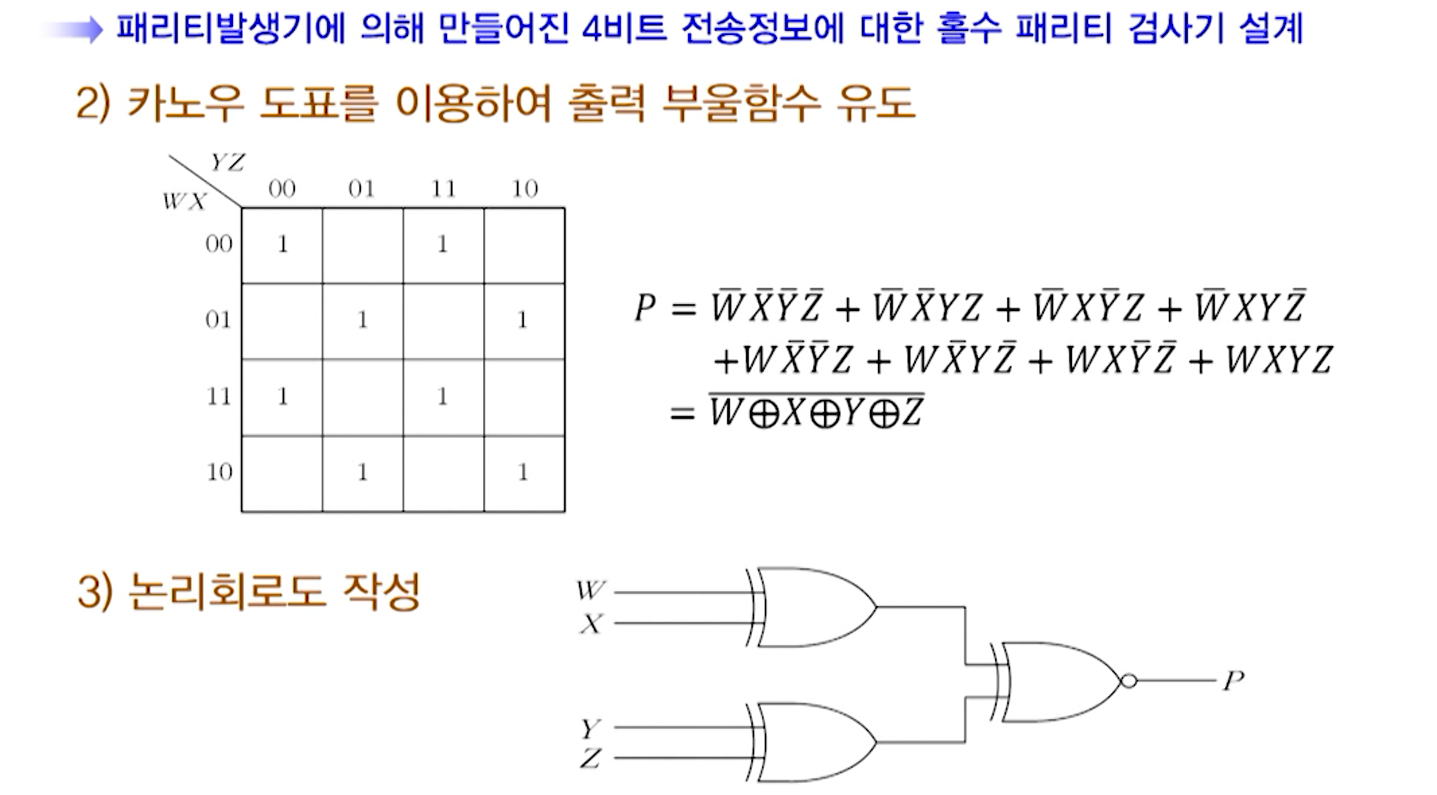

패리티 발생기/검사기

- 발생기

- 검사기

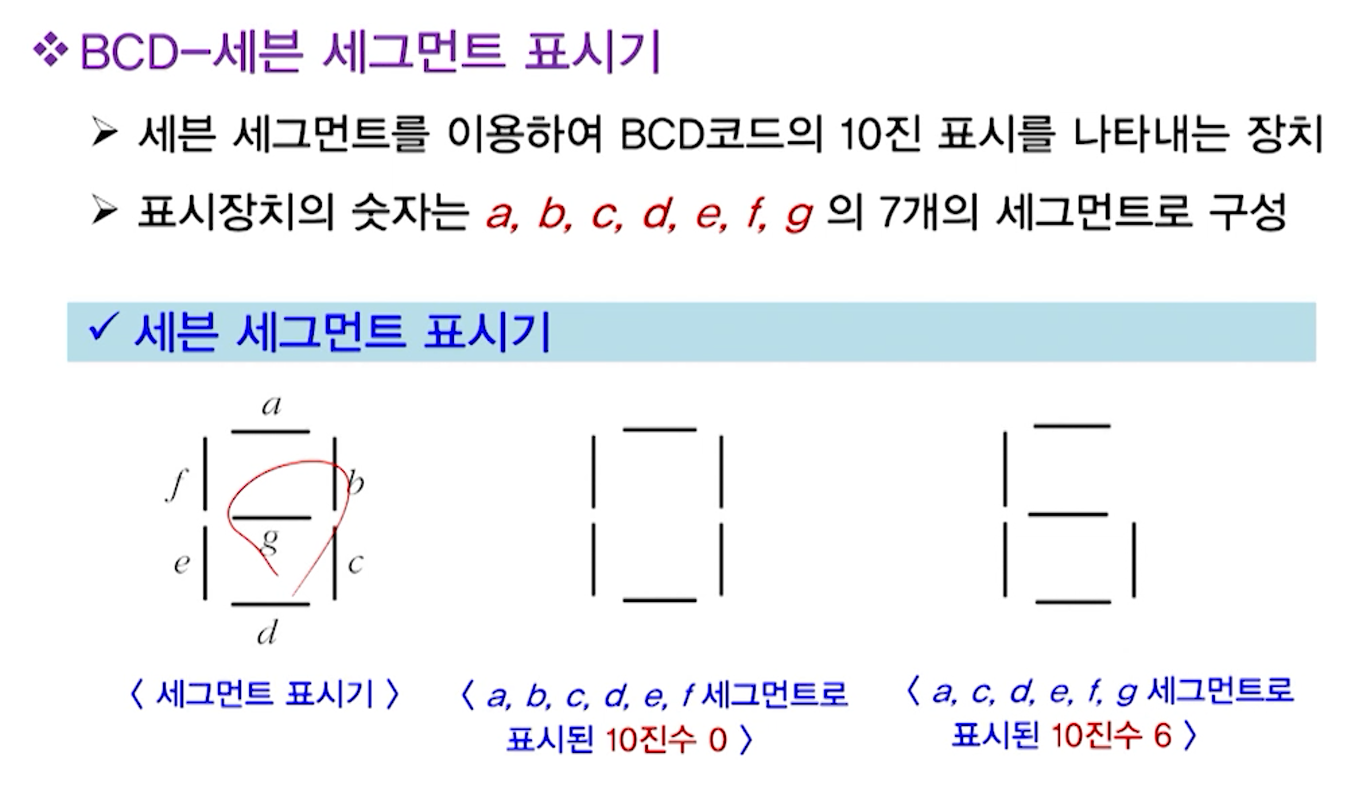

BCD-세븐 세그먼트 표시기

MSI를 이용한 조합논리회로

- 디지털 시스템에서 효과적인 조합논리회로를 설계하기위해서는 주어진 함수를 실현하는데 필요한 게이트의 수를 최소화 필요

- 이를 위해 집적회로(IC) 사용

-> 패키지화된 IC내부의 게이트를 이용하면 경제적인 설계 가능 - 이미 만들어진 MSI정치를 이용하면 다영한 조합논리회로를 설계 가능 -> 인코더, 디코더, 멀티플렉서, 디멀티플렉서

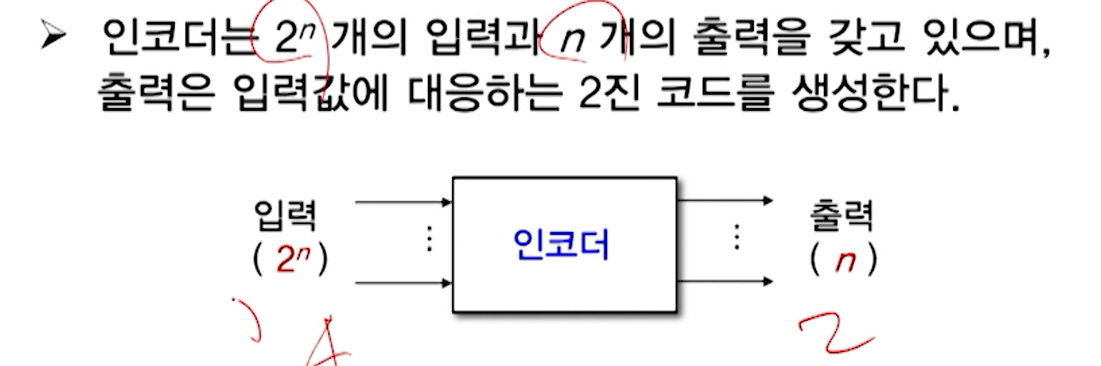

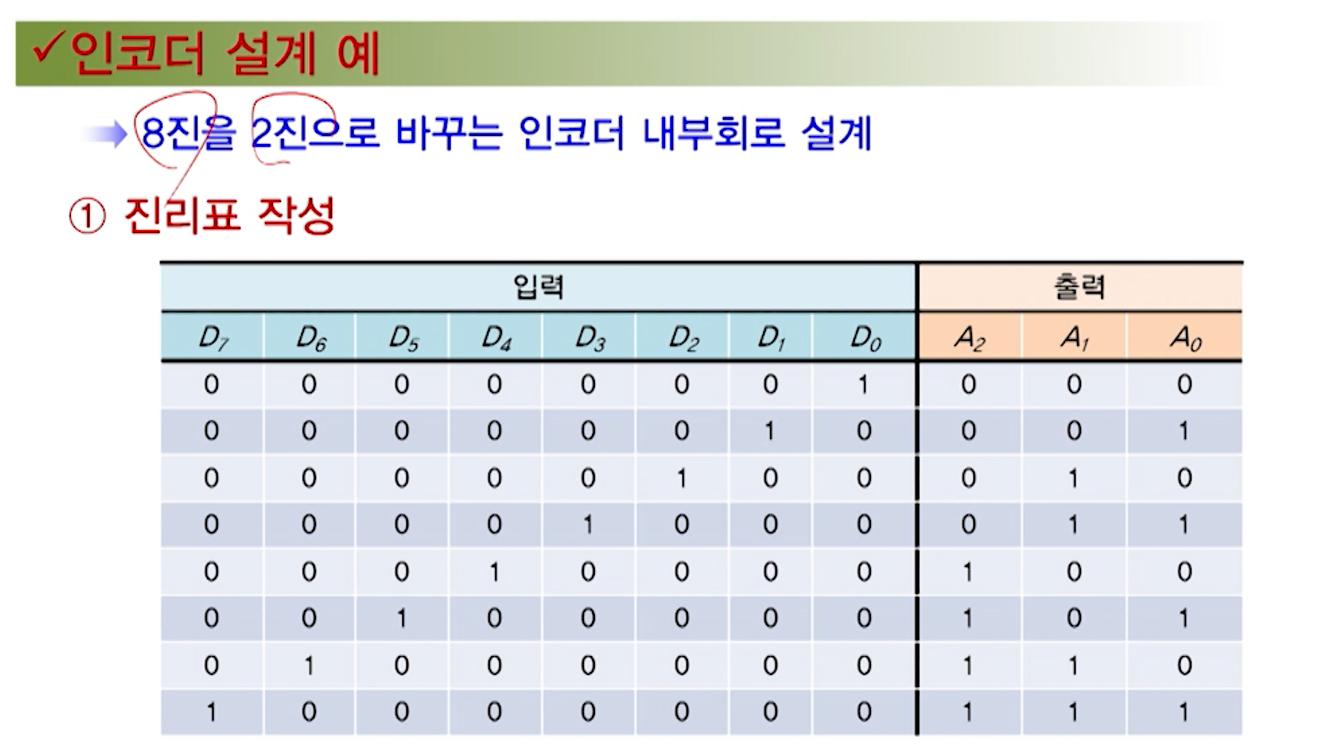

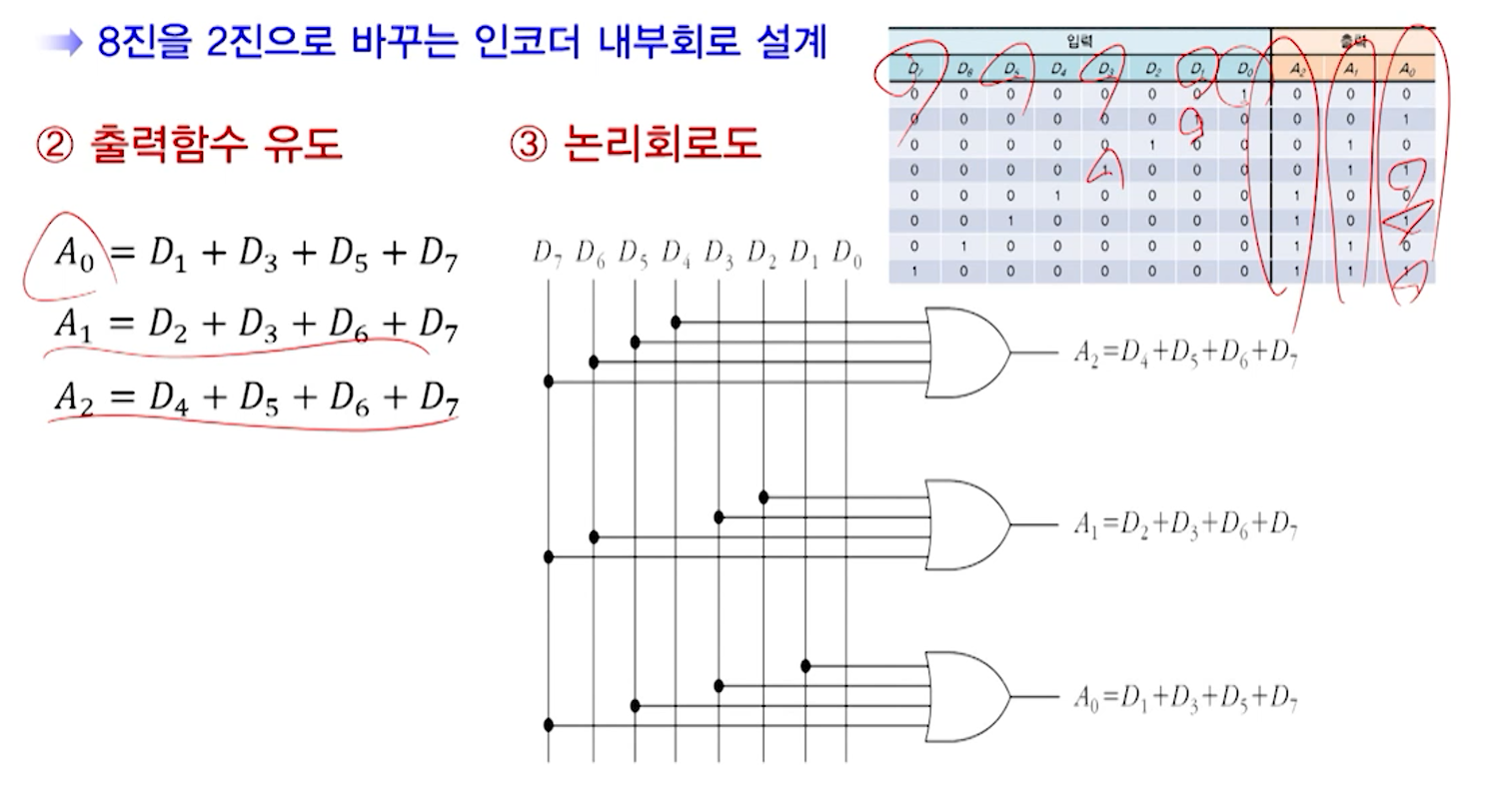

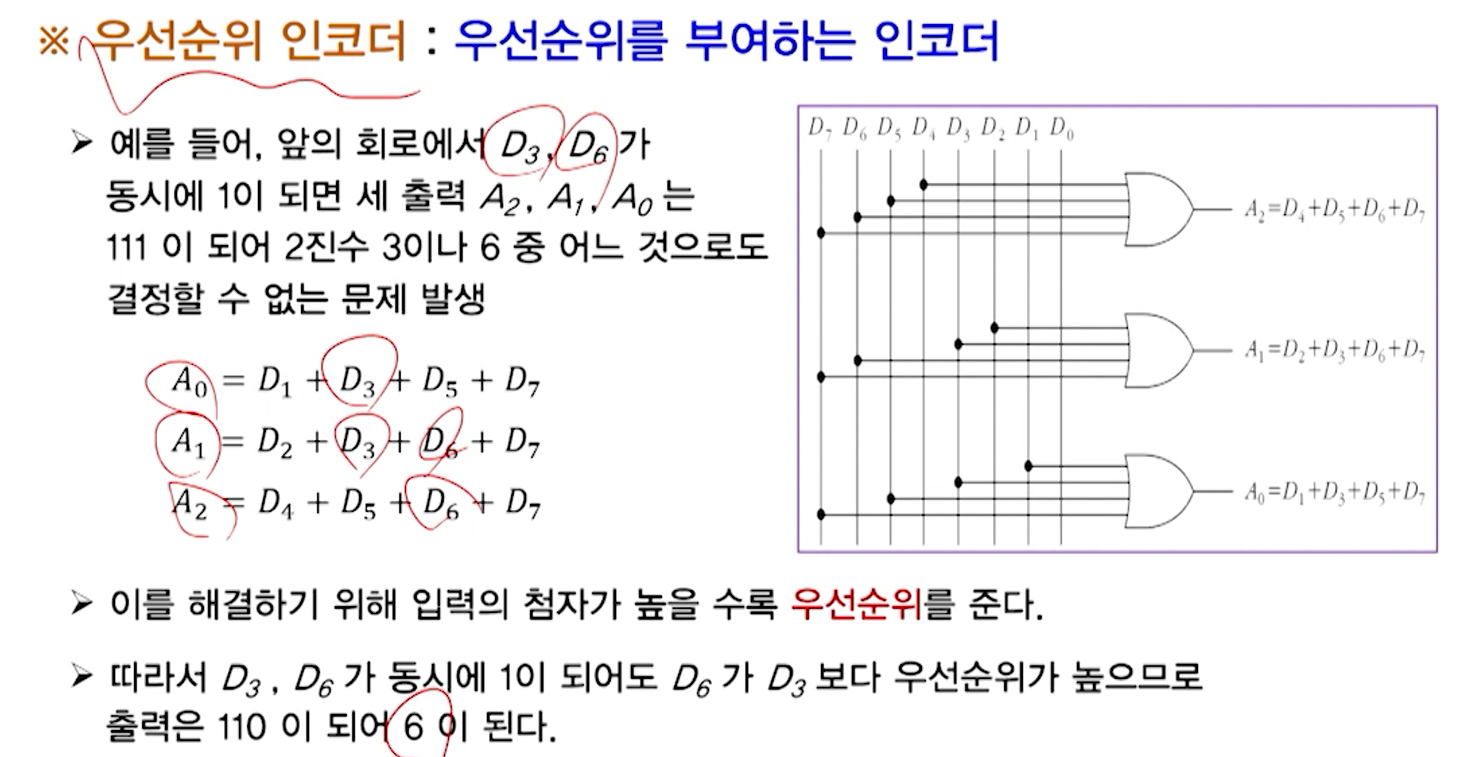

인코더

- 부호화되지않은 입력을 받아서 부호화된 출력을 내보내는 부호화기 예) 10진수나 8진수를 입력으로 받아 2진수나 BCD코드로 변환해주는 조합논리회로