조합논리회로의 분석과 설게

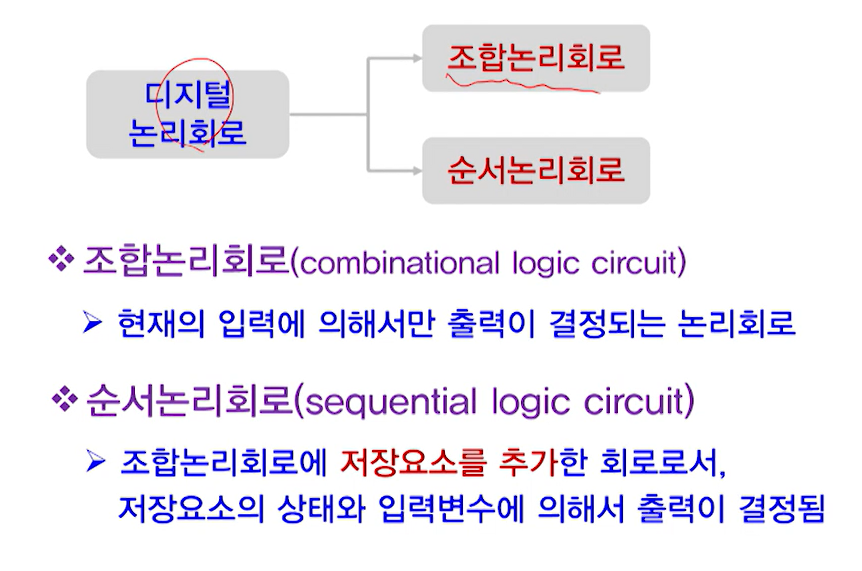

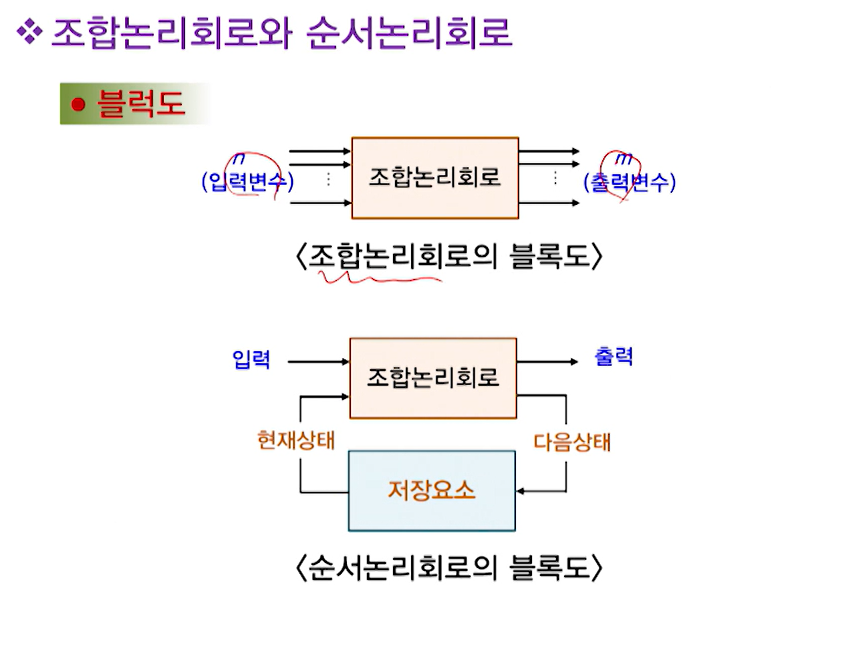

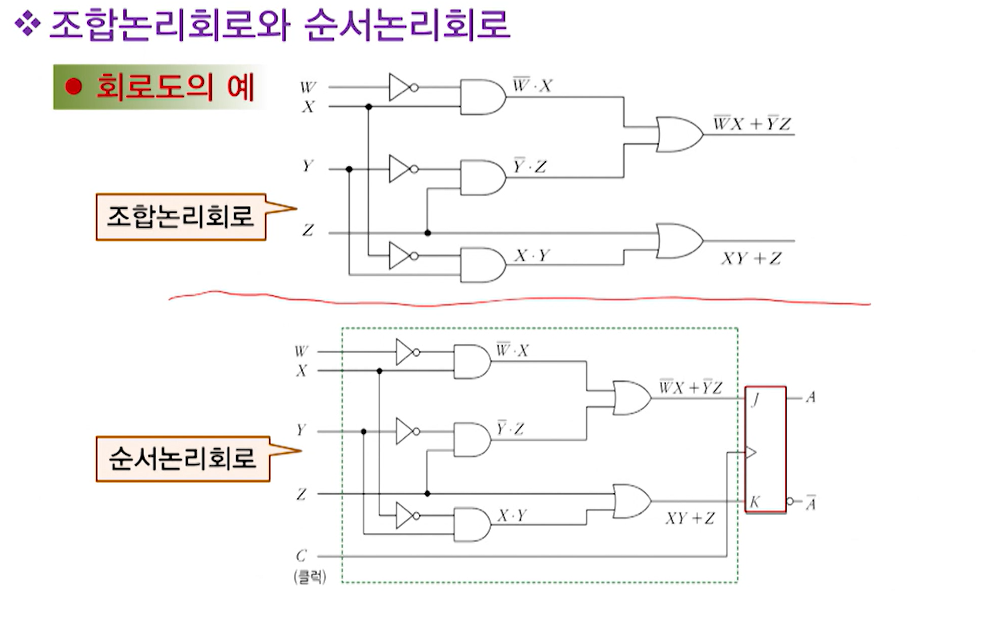

조합논리회로 / 순서논리회로

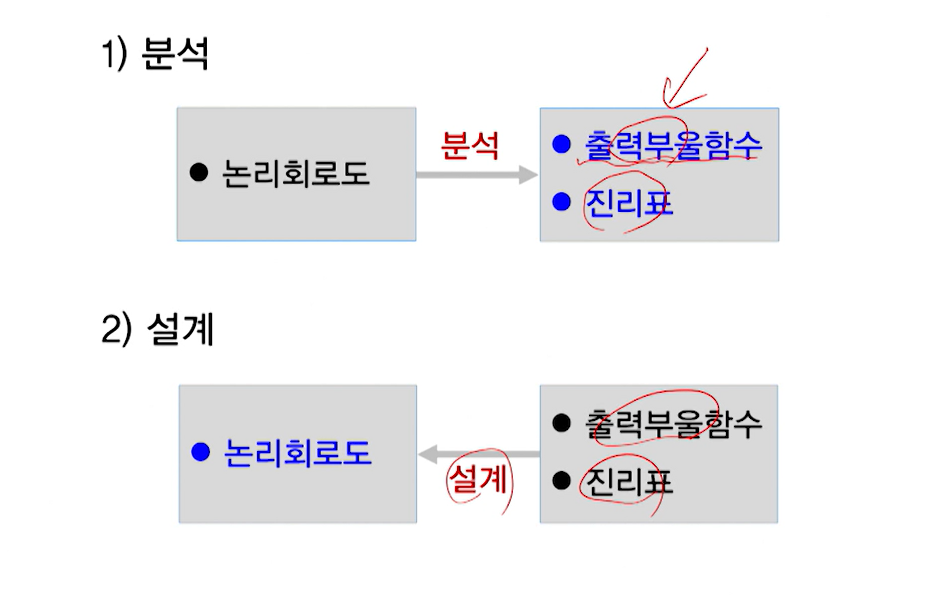

조합논리회로의 분석방법

1. 조합논리회로의 분석

- 주어진 논리회로에서 입출력관계를 구하는 것

- 진리표나 부울함수를 구함으로써 분석이 이루어짐

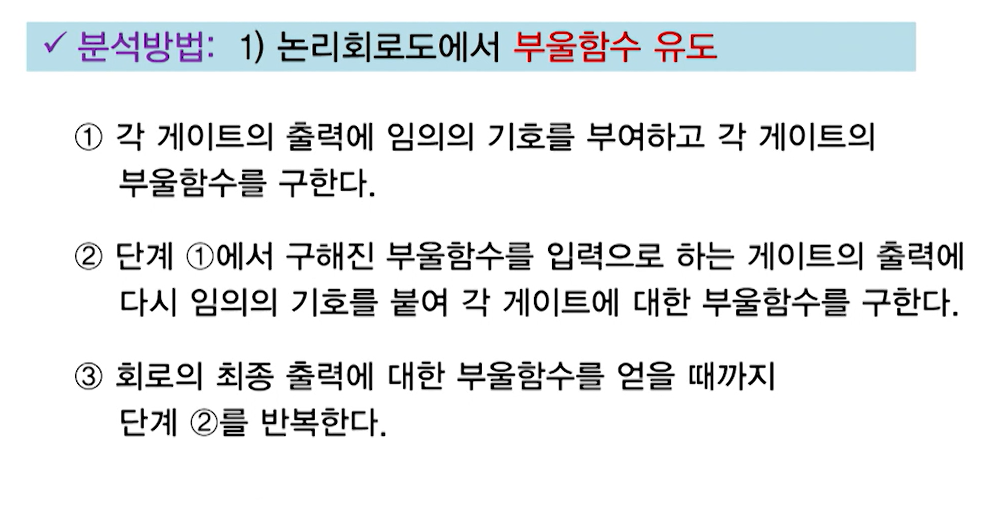

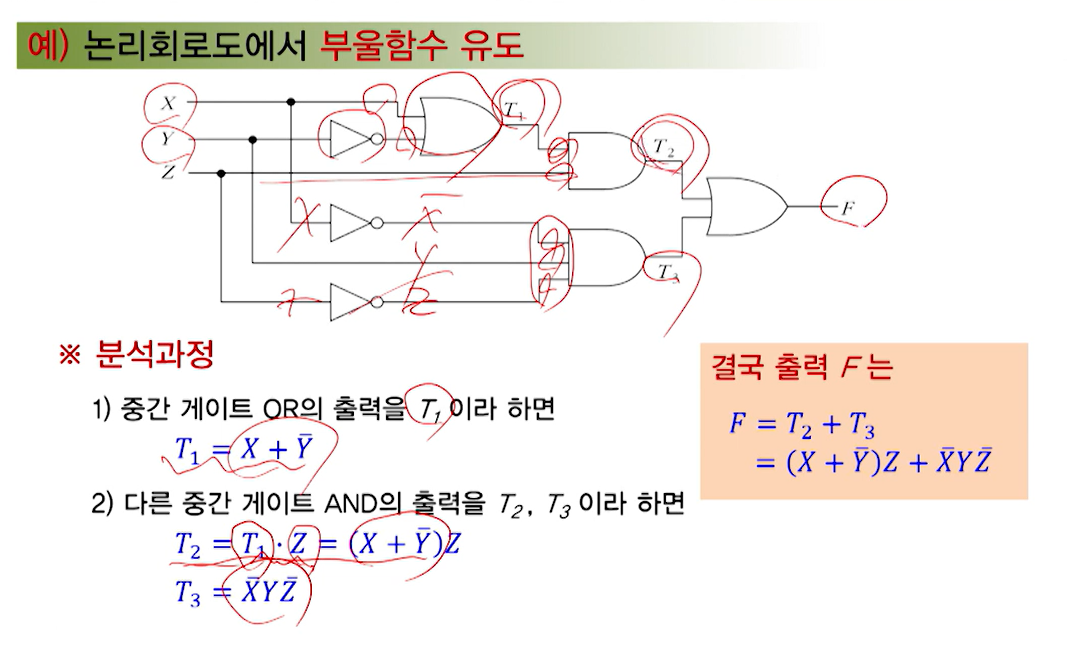

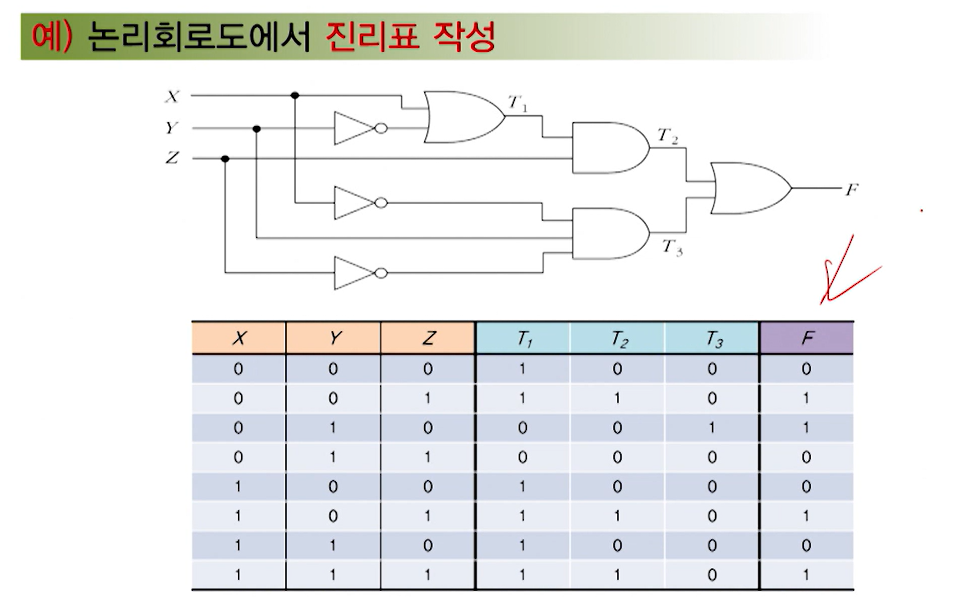

- 분석방법

-

부울함수 유도

-

진리표 작성

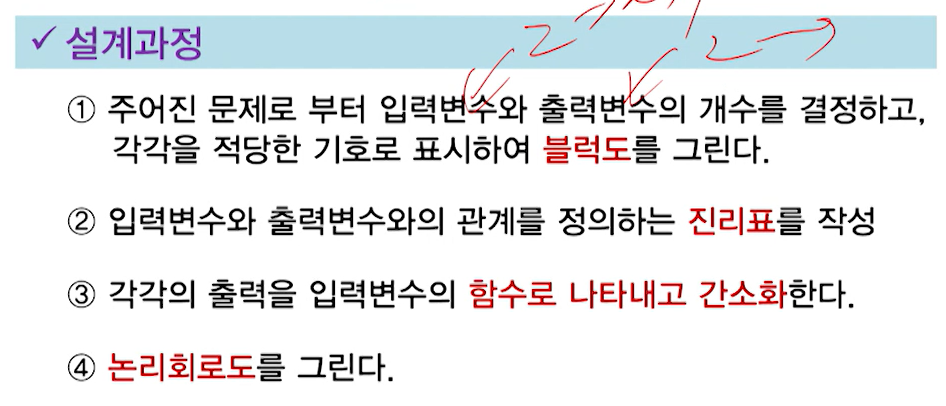

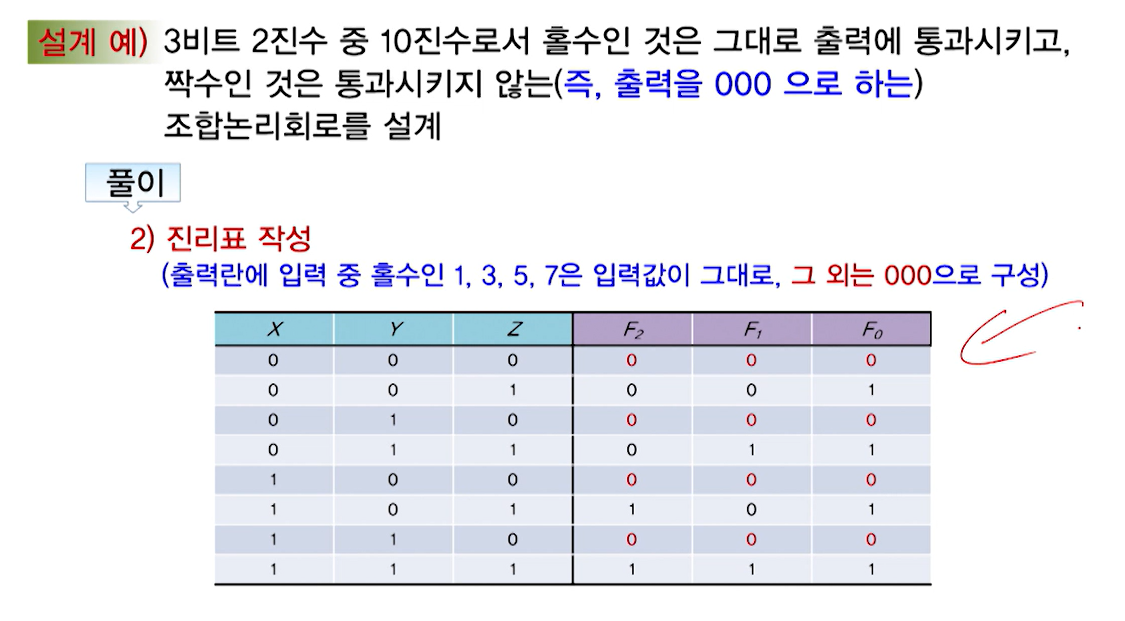

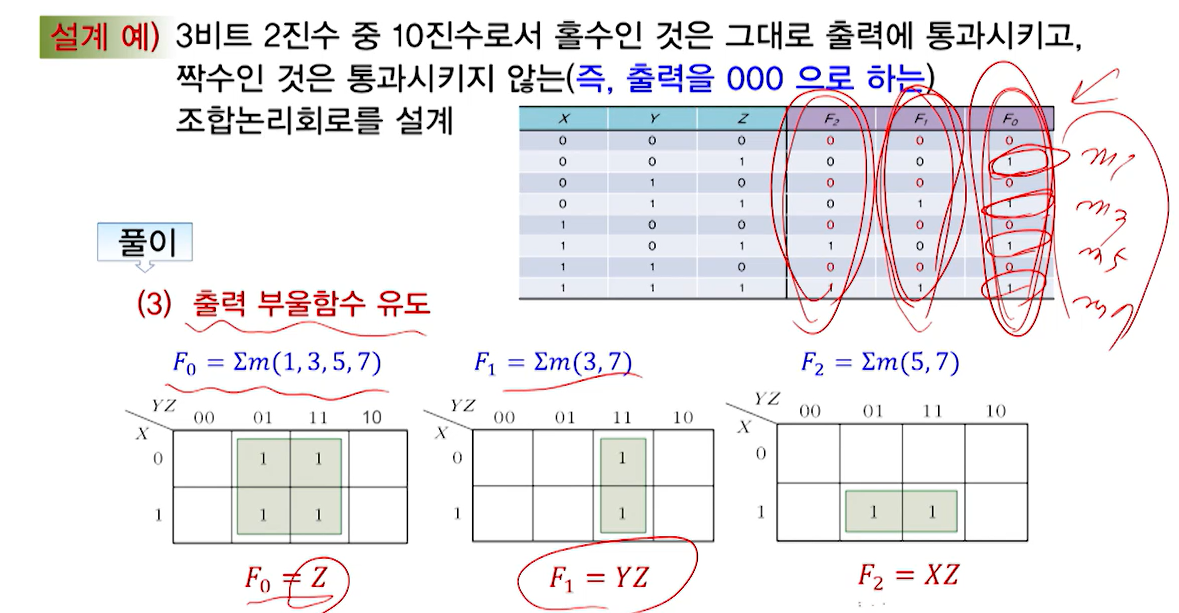

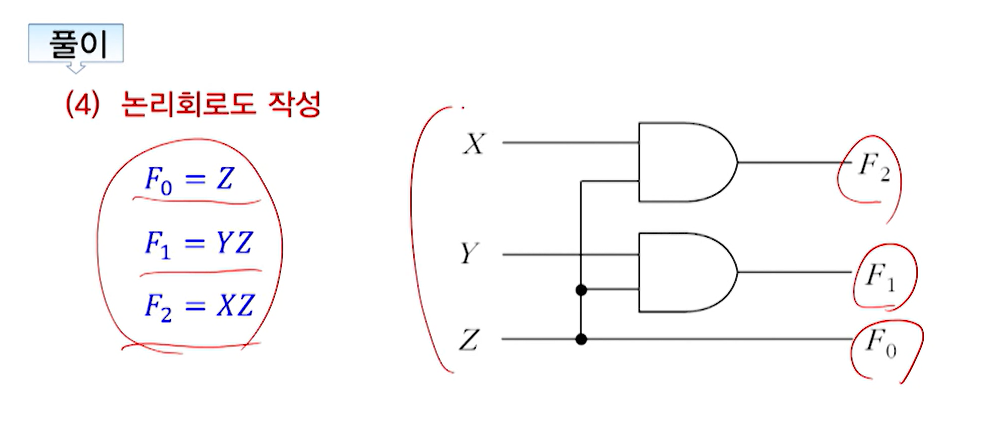

조합논리회로의 설걔방법

- 조합논리회로의 설계

- 문제에 대한 설명으로부트 논리회로도나 논리회로를 작성할 수 있는 부울함수를 구하는 과정

기본연산회로

- 가/감/승/제의 산술연산회로

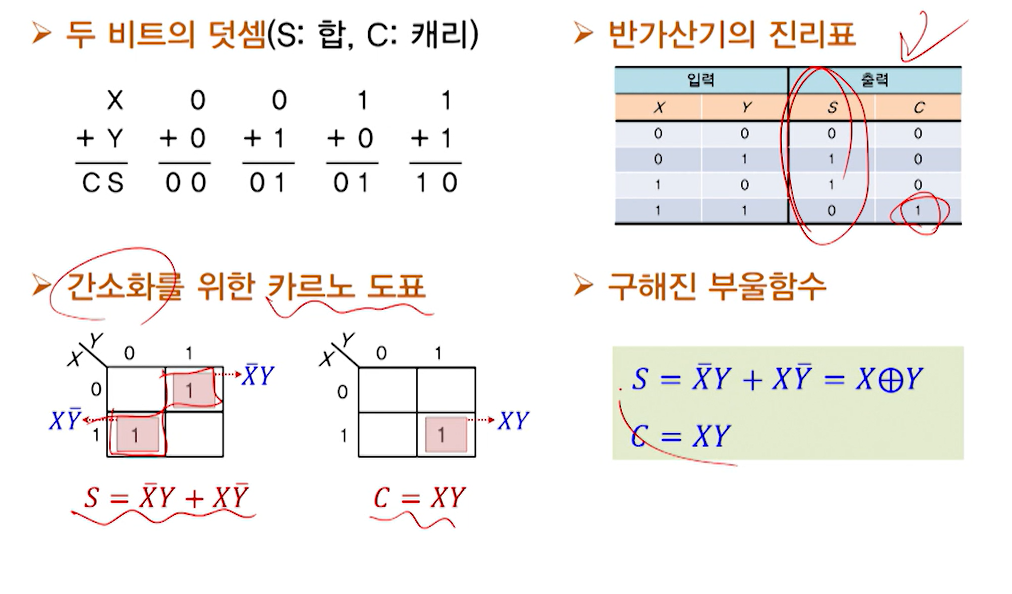

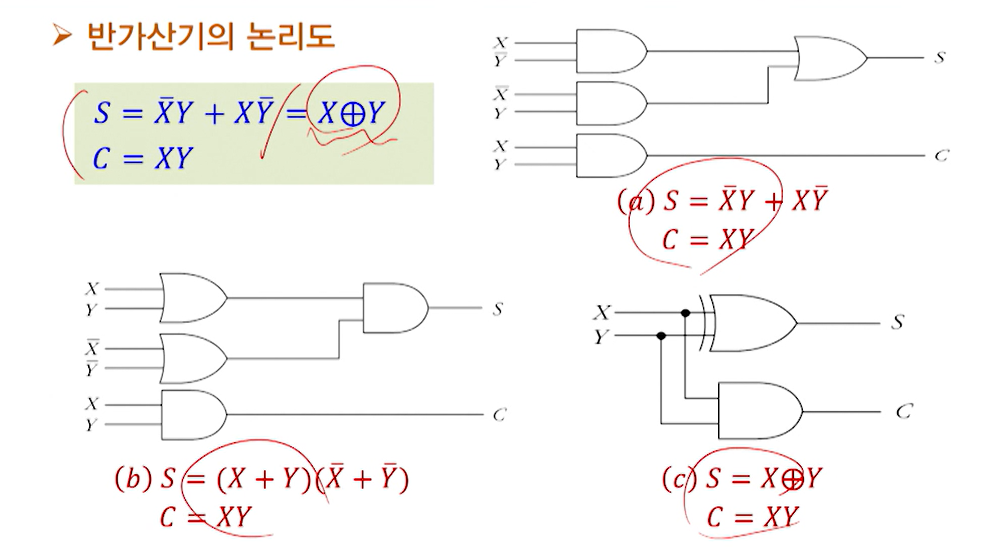

가산기

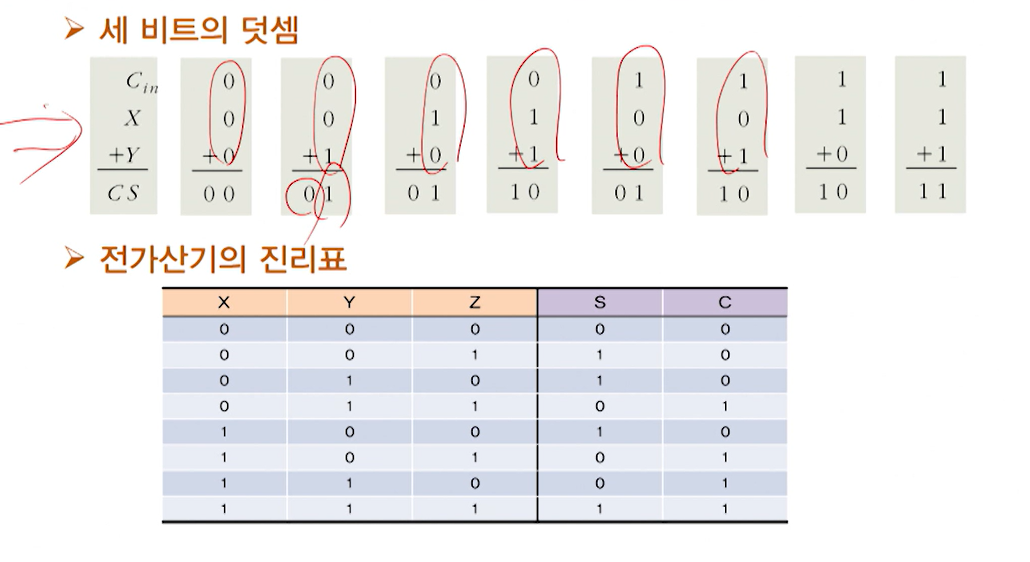

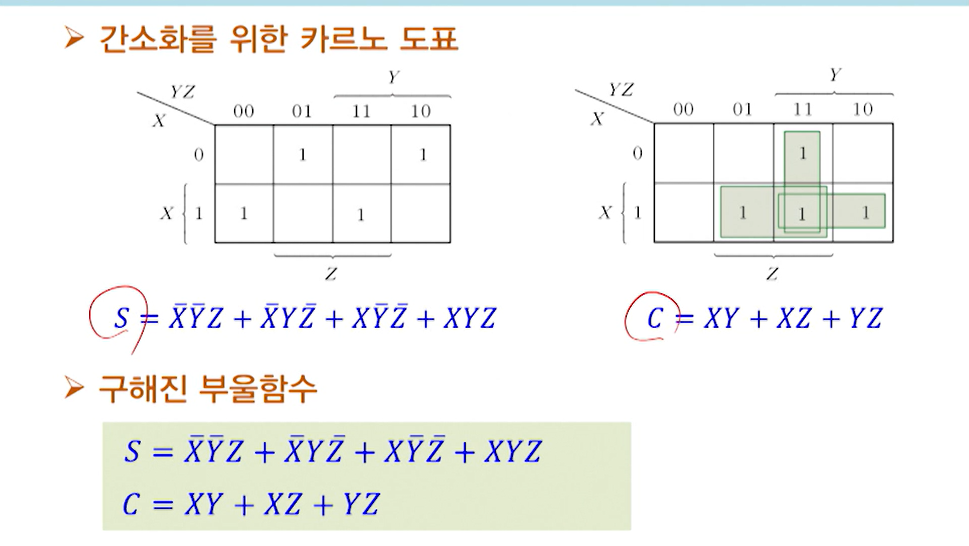

- 2진수의 덧셈을 수행하는 조합논리회로

- 반가신기(HA) : 두비트의 덧셈을 수행

- 전가산기(FA) : 세비트의 덧셈을 수행

반가신기

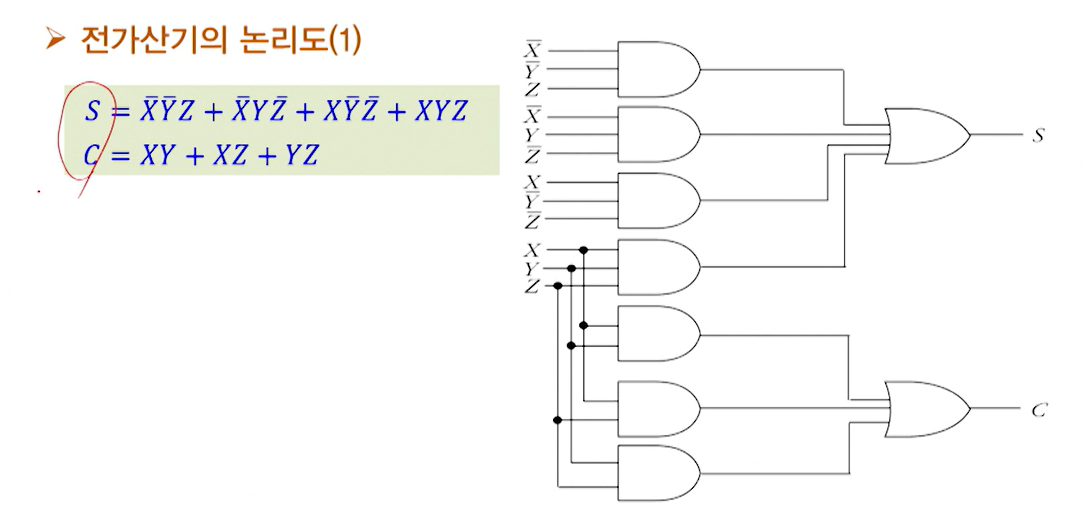

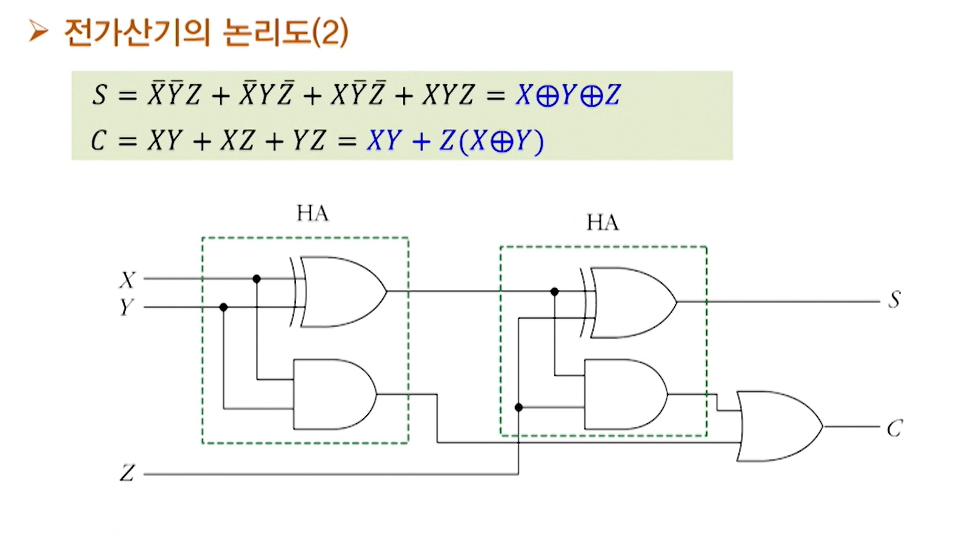

전가산기

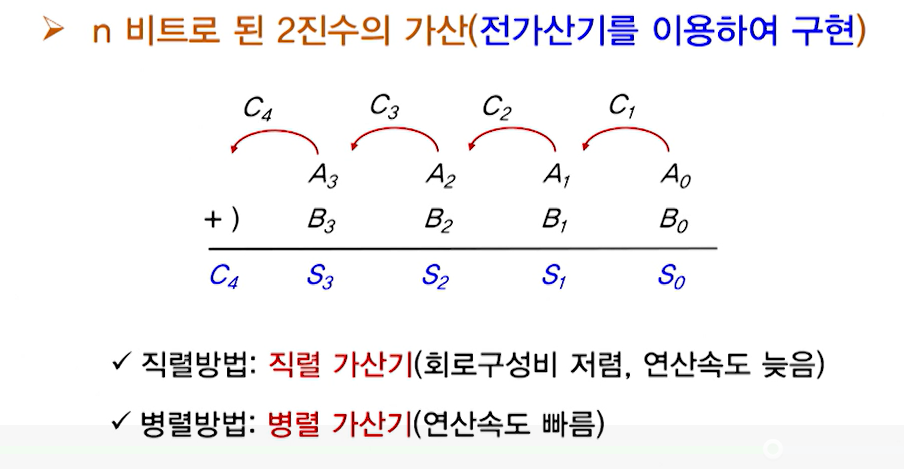

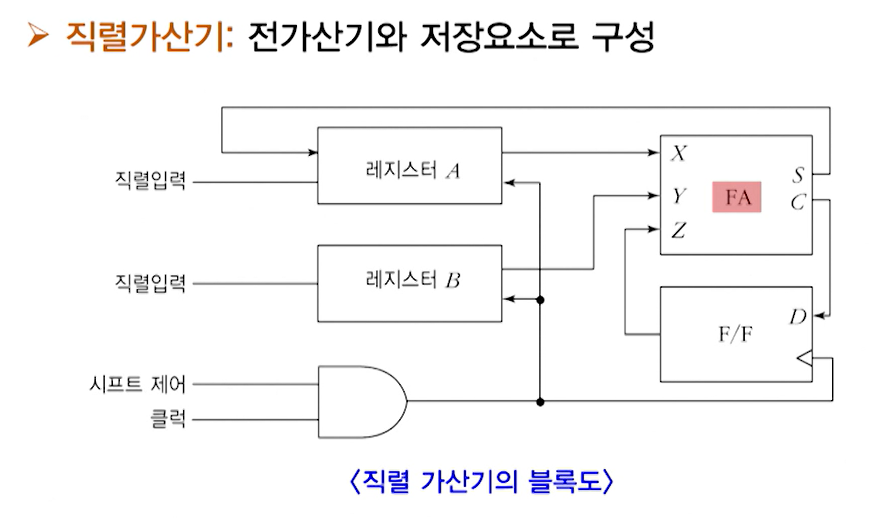

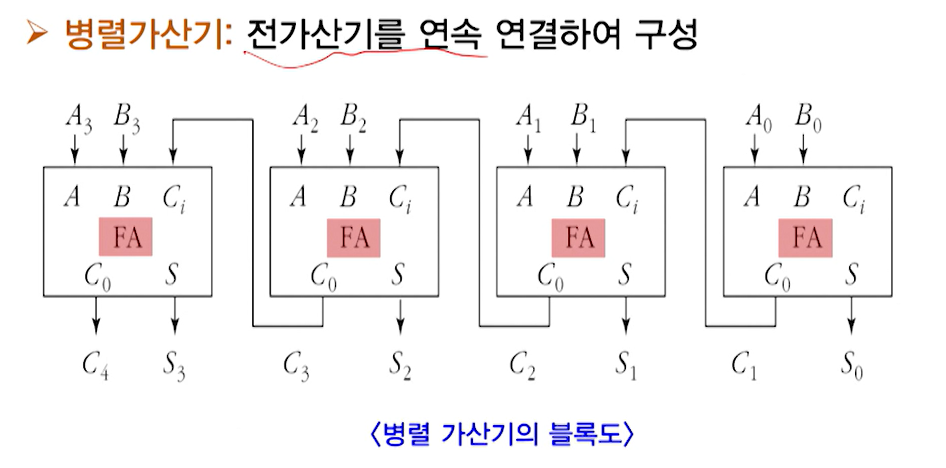

직/병렬 가산기

-

직렬 가산기

-

병럴 가산기

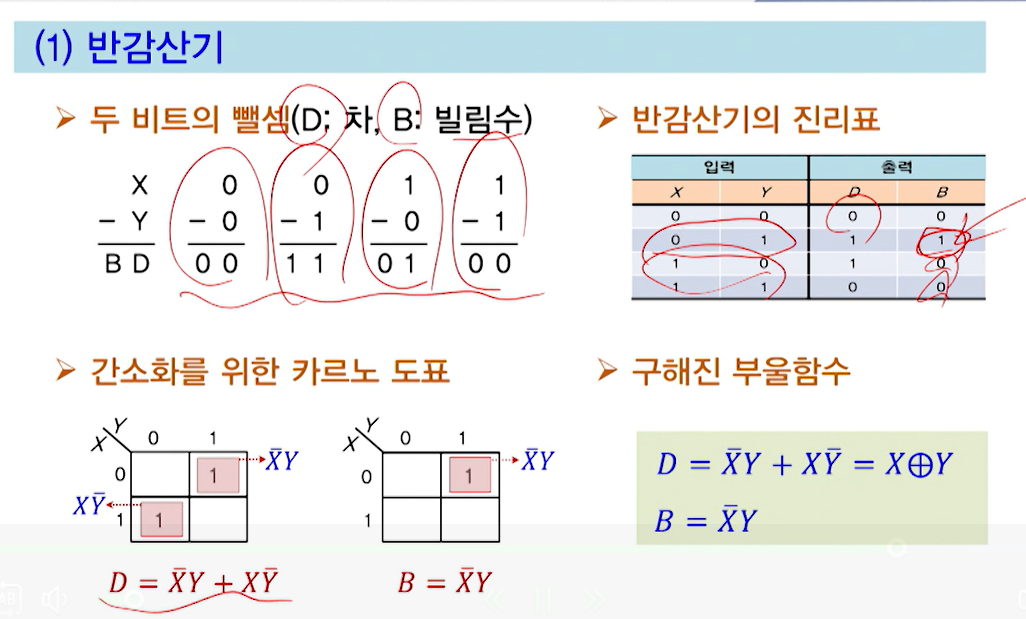

감산기

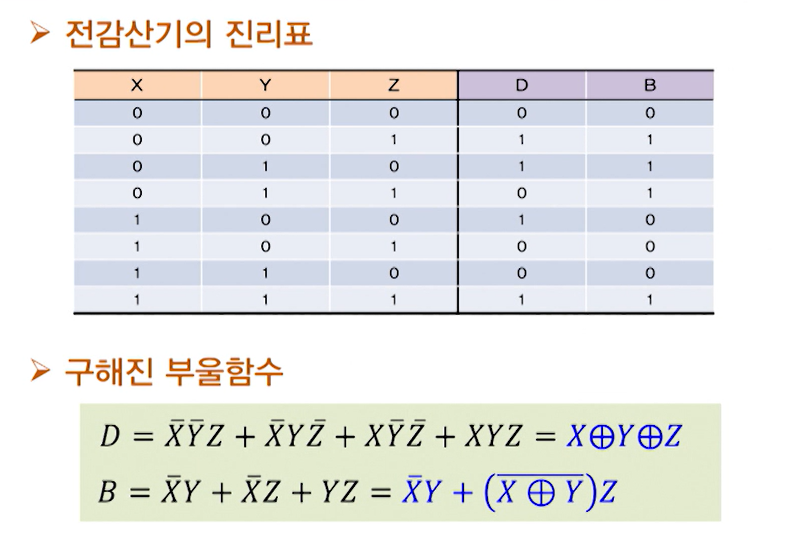

- 2진수의 뺄셈을 수행하는 조합논리회로

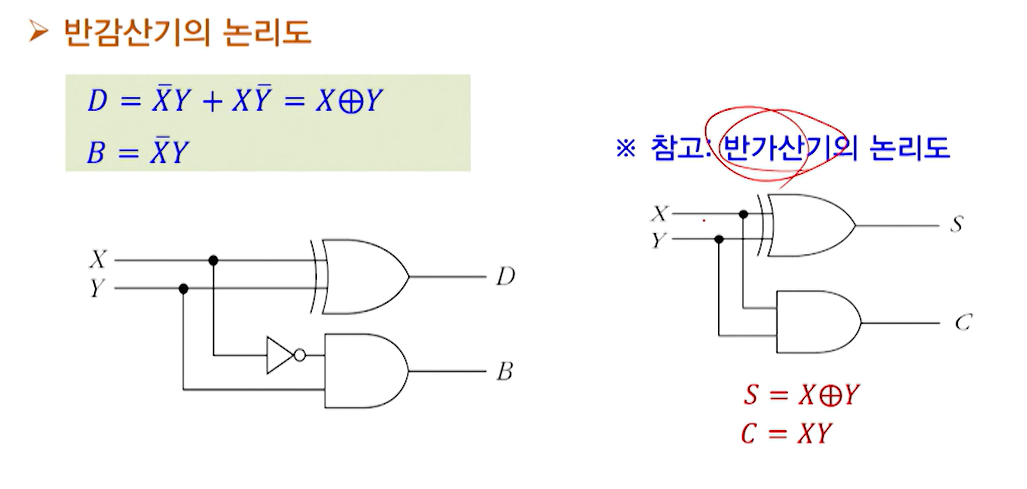

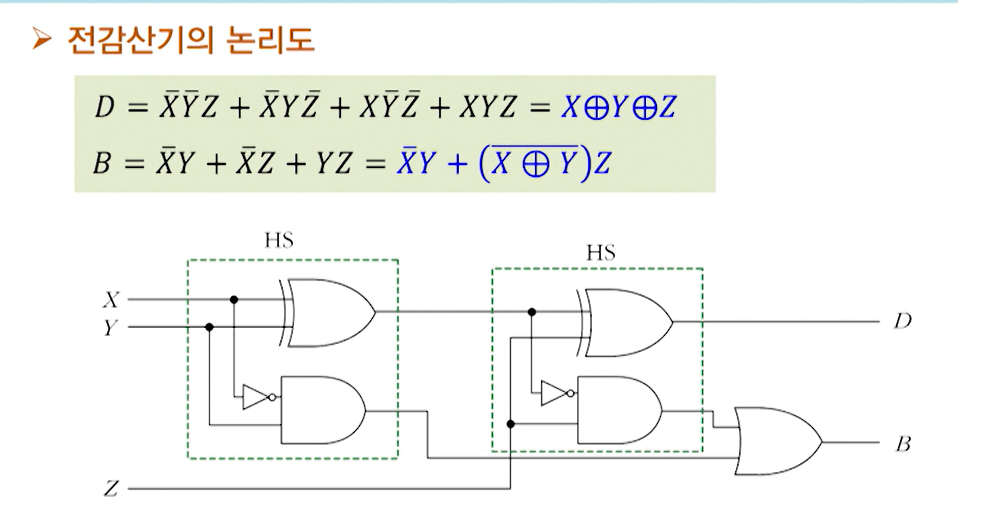

- 반감산기(HS) : 두비트의 뺗셈을 수행

- 전감산기(FS) : 세비트의 밸셈을 수행

반감산기

전감산기

-> HA에 not gate 추가돼서 HS 됨

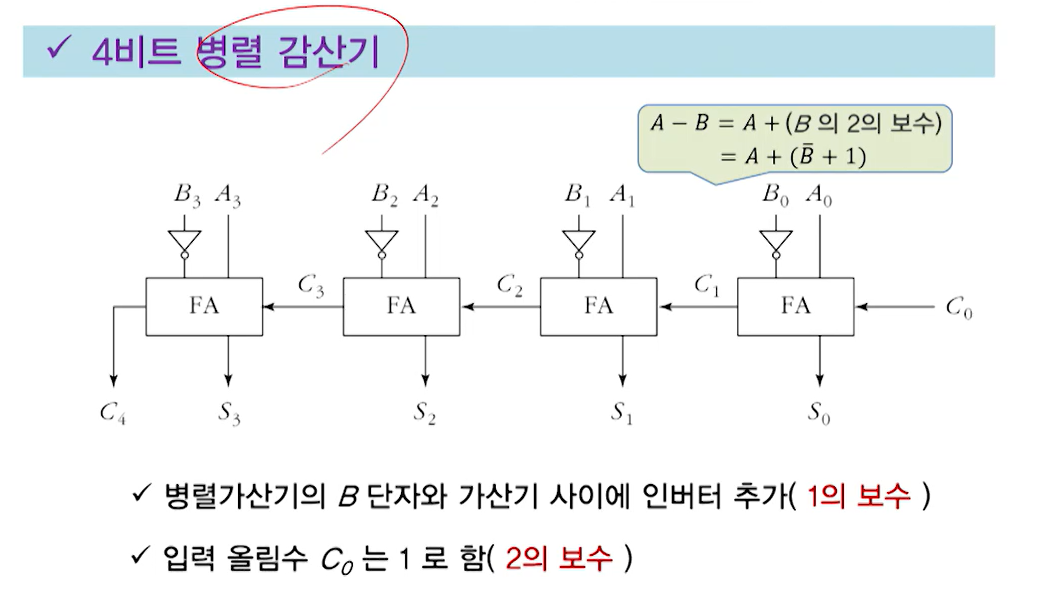

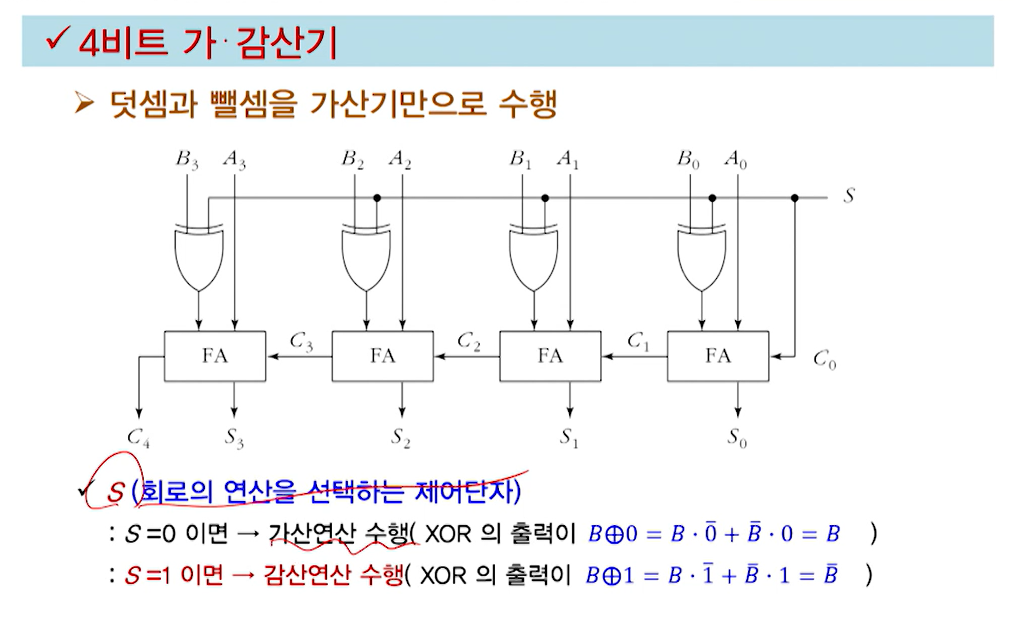

병결 가/감산기

- 2진 감산

- 가산기를 사용하여 수행 - 까산기만을 사용하기 때문에 전체 회로를 최소화 가능

- A-B의 감산

- B의 2의 보수를 취하여 A에 더한다 : 이때 2의 보수는 1의 보수를 취한 값의 최소 유효비트에 1을 더해 구함

- 회로에서 1의 보수는 인버터를 이용하면 구할 수 있고 가산기에서 입력 올림수를 1로하면 합의 값에 1을 더할 수 있으므로 2의 보수가 된다.

-> B에 not 게이트 추가한 것 확인

-> s가 0일때는 가산기, 1일때는 감산기로 작동