시간표현과 상태 기억

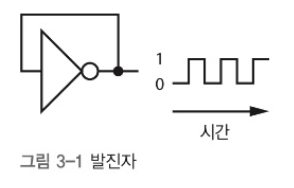

발진자

인버터를 사용해서 다음과 같이 출력을 입력에 연결할 수 있다.

- 이런 식의 연결을 되먹임(feedback)이라 한다.

- 인버터의 출력은 다시 인버터 입력으로 들어가며, 이 입력은 다시 출력에 반영된다. 이로 인해 출력이 0과 1사이를 진동하게 된다.

진동 속도는 전파 지연나 온도에 따라 달라지는 경향이 있다.

클록

발진자는 컴퓨터에 클록(clock)을 제공한다. 클록은 회로의 페이스(pace)를 결정하며, 회로의 최대 클록 속도나 가장 빠른 템포는 전파 지연 시간에 의해 결정된다.

컴퓨터 컴포넌트 제작에는 지연 시간을 기준으로 빈들을 분류하여 부품 전체의 편차보다는 더 작은 편차를 갖도록 부품을 빈에 나눠 담는다.

컴포넌트 : 프로그래밍에 있어 재사용이 가능한 각각의 독립된 모듈

생산자는 빈의 전형적인 값과 함께 최댓값과 최솟값을 제공한다.

참고

오버클로킹 : 빈의 중간 정도에 위치하는 부품들이 부품이 고장나지 않을 범위 내에서 클록을 빠르게 공급하는 것

래치

클록을 통해 시간을 표현할 수 있으므로 1비트를 기억하는 방법을 생각해보자.

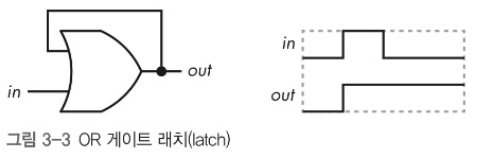

OR 게이트의 출력을 입력에 묶는 방식의 피드백을 사용하면 이전 정보를 기억할 수 있다.

- 자신의 과거 상태를 기억한다.

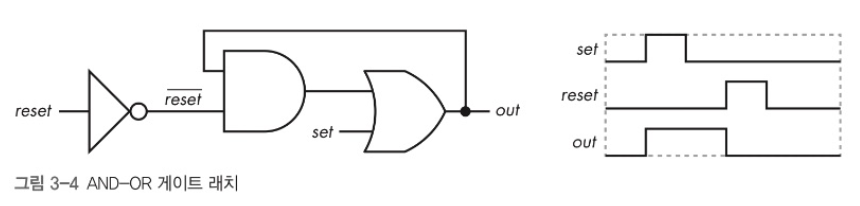

그러나, 이 회로는 out을 다시 0으로 만들 수 있는 방법이 없기에 약간의 추가 작업이 필요하다.

- reset bar(reset 위에 바가 있는 것)는 반전을 의미

- 값이 0인 경우 참(활성화 상태)이며 이 상태를 엑티브 로우(active low)라 한다.

- AND 게이트를 통해 피드백이 깨지고 out은 0이 될 수 있다.

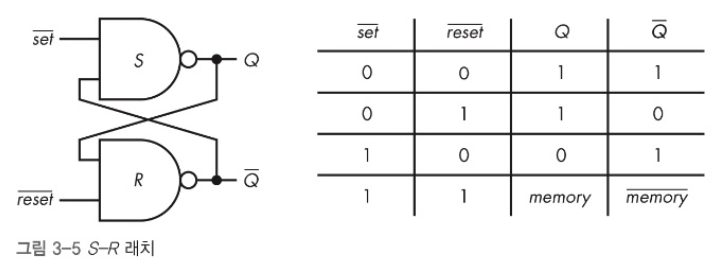

이 방법말고 더 똘똘하게 1비트 메모리를 만드는 방법이 있다. S-R(Set-Reset) 래치를 통해 이들은 엑티브 로우 입력을 받고 보수 출력을 제공한다.

보수출력 : 한쪽은 엑티브 하이, 다른 쪽은 엑티브 로우인 경우

- 두 입력(set bar와 reset bar)이 모두 참(로우)인 경우에는 두 출력이 모두 참이라서 이상하기 때문에 이런 입력은 사용하면 안된다.

- 두 입력(set bar와 reset bar)이 모두 거짓(하이)인 경우에는 전파 지연시간에 따라 출력이 달라지기 때문에 결과를 예측할 수 없다.

- 회로가 대칭적이라 set, reset 신호의 지연 시간이 거의 비슷하다.

참고

NOR 게이트를 통해서도 S-R 래치를 만들 수 있지만, NAND에 비해 비용이 비싸며 전력 효율이 떨어진다.

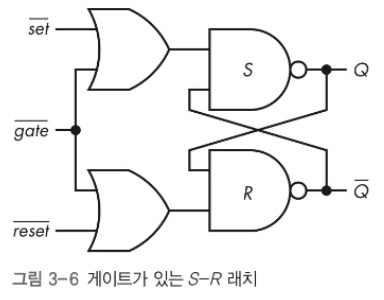

게이트가 있는 래치

이제 정보를 기억할 방법이 있으므로, 어느 시점에 무언가를 한다는 것이 어떤 뜻인지 살펴보자.

- gate bar 입력이 거짓(하이)인 경우 set bar와 reset bar가 어떤 값이든 OR 게이트 출력이 모두 1이되므로 관계가 없다.

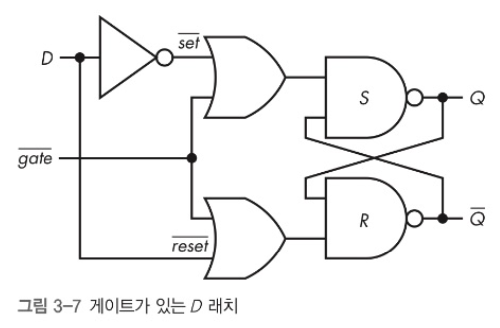

1비트 정보를 유지하고 싶기 때문에 다음으로 이 회로를 개선할 수 있는 방법은 다음과 같다.

- set bar와 reset bar를 같은 입력에 연결하면서 한쪽 입력에는 인버터를 추가해서 입력을 1비트만 받게 만든다.

- 이 1비트 입력을 D라고 한다.

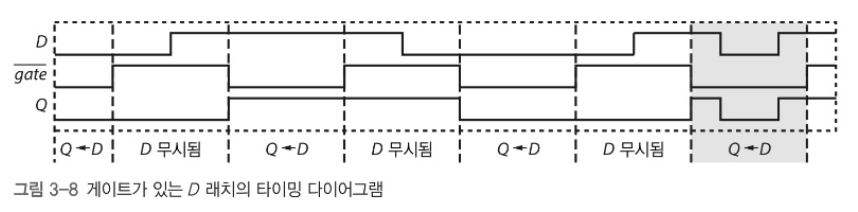

이제 gate bar = 1(참, 로우)일 때 D = 1이면 Q = 1이다. gate bar = 1(참, 로우)일 때, D = 0이면 Q = 0이다. gate bar = 1(참, 로우)인 상태에서는 D의 변화가 그대로 출력(Q)에 나타난다.

gate bar = 0(거짓, 하이) 일 때는 D가 변해도 Q 출력에 아무 변화가 없다.

이 출력의 문제는 앞서 봤던 gate bar = 1(참, 로우)인 경우 D = Q인 것이다. 이로 인해 우리는 D가 '예의 바르게 행동'해서 '게이트'가 '열려 있는' 동안에는 스스로의 상태를 바꾸지 않기를 바랄 수 밖에 없다.

이런 게이트를 여는 시간을 최소화해서 거의 순간적으로 D의 상태에 맞춰 출력 상태를 변경할 수 있다면 좋을 것이다.

플립플롭

앞서 언급했던 것 처럼 데이터 변경으로 인해 잘못된 결과가 생길 수 있는 가능성을 최소화하고 싶다.

이에 가장 일반적으로 사용되는 방법이 에지(edge)이다.

에지(edge)

- 논리 수준이 특정 값에 머무는 동안 데이터를 잡아내지 않고 논리 수준이 한 수준에서 다른 수준으로 전이되는 중간에 데이터를 잡아내는 방법

- 이를 시간에 대한 판정 기준이라 생각할 수 있다.

다음 그림을 보면 논리 수준 사이의 (0 to 1 또는 1 to 0) 전이가 거의 순식간에 벌어진다는 사실을 알 수 있다.

애지에 의해 데이터 변화가 촉발되는 래치를 플립플롭(flip-flop) 이라 하며, 이는 1비트의 정보를 기억할 수 있는 최소의 기억소자다.

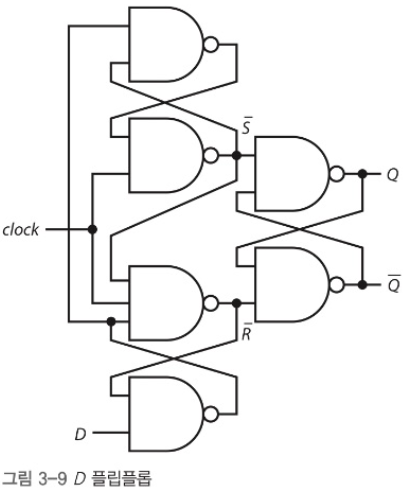

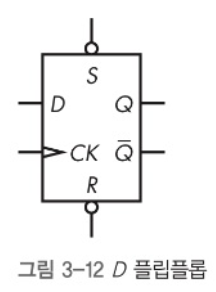

플립플롭을 만들 때는 래치를 기본 요소로 사용한다. 3개의 S-R 래치를 다음 그림처럼 잘 연결하면 양의 에지에 의해 변화가 촉발되는(positive edge-triggered) 플립 플롭을 만들 수 있으며, 이를 D 플립플롭이라 부른다.

양의 에지에 의해 변화가 촉발되는(positive edge-triggered)

- 0 에서 1로 바뀌는 순간에 플립플롭의 출력이 바뀐다는 뜻

- 반대로 음의 에지에 의해 변화가 촉발되는 플립플롭은 1에서 0으로 갈 때 출력이 바뀐다는 것을 의미한다.

- S-R 래치에 인버터(Not 게이트)를 연결한 형태

- clock(CK)의 시간 간격만큼 지연시켜 출력한다.

- 입력값과 출력값이 동일하다.

-

D Q(t + 1) 0 0 1 1

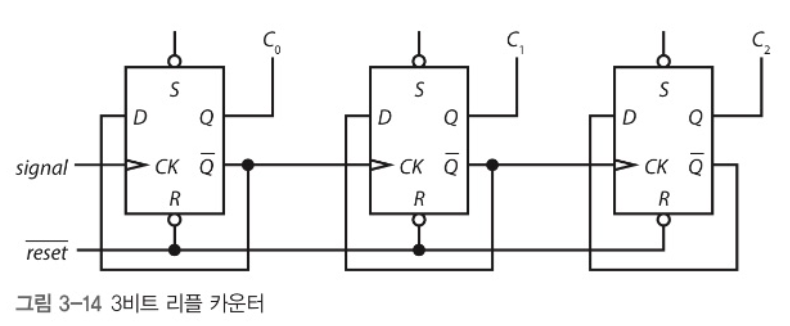

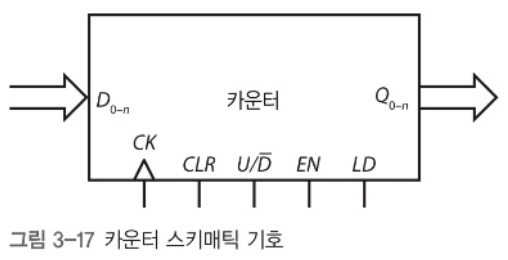

카운터

플립플롭을 응용하여 1, 2, 3 순서대로 수를 세주는 카운터가 있다.

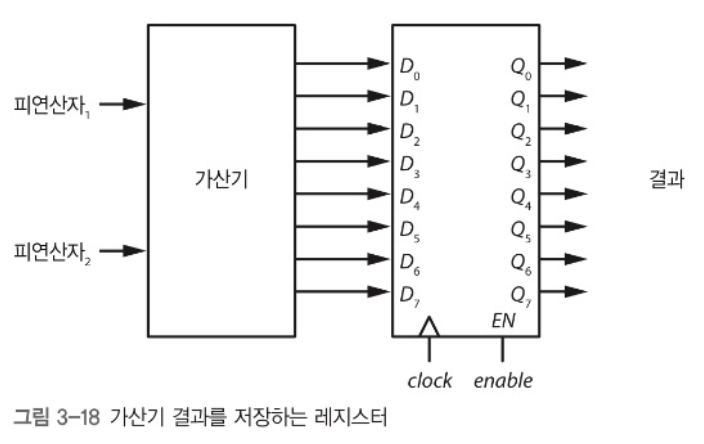

레지스터

값을 기억하기 위해 사용하는 D 플립플롭을 응용하여 여러 비트를 저장할 수 있는 회로인 레지스터를 구현할 수 있다.

메모리 조직과 주소 지정

앞의 내용에서 이것들을 기억하자.

- 플립플롭 : 1개의 비트를 기억할 때 유용

- 레지스터 : 여러 비트를 기억할 때 유용

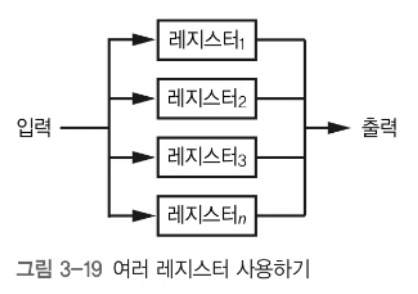

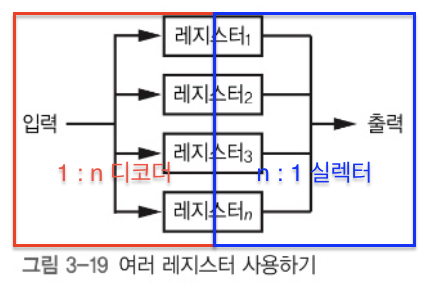

만약, 훨씬 많은 정보를 기억해야한다면 어떻게 할까? 간단하다. 여러 레지스터를 사용하면 된다.

그러나, 여러 레지스터를 사용하면 출력시 어떤 레지스터를 사용해야 하는가에 대한 문제에 직관한다.

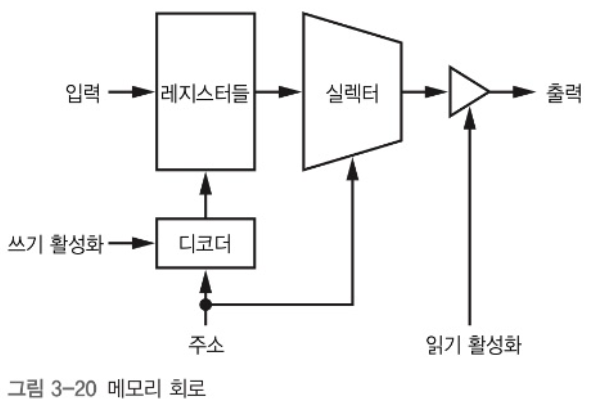

각 레지스터에 번호(주소)를 부여한 후 디코더를 기본 요소로 사용하면 이를 해결할 수 있다. 출력을 선택할 때는 실렉터를 사용하면 된다.

이 요소들을 합치면 메모리 컴포넌트가 만들어진다.

- 한눈에 봐도 꽤 복잡하다.

- 다뤄야할 비트 수가 커질수록 연결해야 되는 요소들도 증가한다.

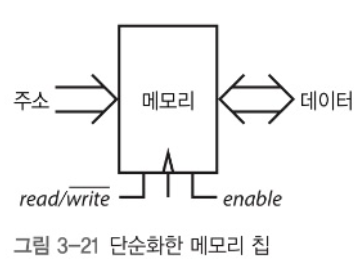

메모리를 동시에 읽고 쓸 필요가 거의 없다는 사실에 기반에 연결을 줄일 수 있다. 입력과 출력 데이터 연결을 합치고 read/write bar 제어 신호를 사용하면 연결을 많이 줄일 수 있다.

- 큰 화살표는 연관된 신호를 의미하는 버스이다.

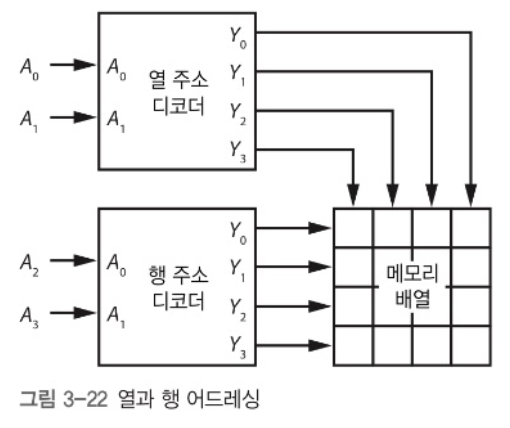

메모리 칩 내부는 격자로 되있으며, 내부 위치들은 다음과 같이 행과 열을 조합해서 지정된다.

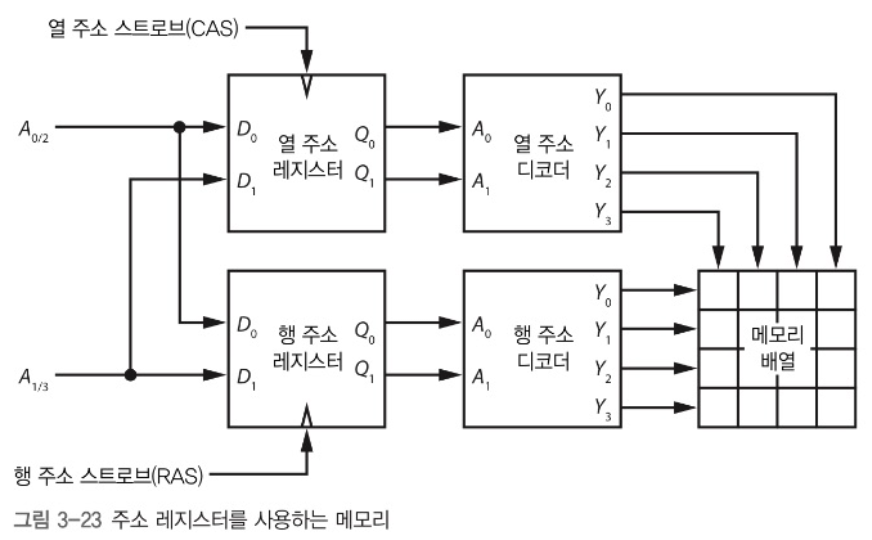

주소가 두 부분으로 나눠 들어오기 때문에, 한 번에 한 부분만 변경할 수 있다면 성능이 더욱 좋아진다. 예를 들어, 행 주소를 먼저 지정하고 열 주소만 변화시킨다면 좀 더 빨리 처리할 수 있다.

행과 열 주소를 멀티플렉싱하면 주소 라인의 수를 절반으로 줄일 수 있다.

임의 접근 메모리(RAM)

지금까지 살펴본 메모리를 임의 접근 메모리(random access memory, RAM)이라 한다. RAM을 사용하면 메모리 위치중 어디든 원하는 순서대로 쓰거나 읽을 수 있다.

RAM의 종류는 크게 2가지이다.

- DRAM

- 가격이 저렴

- 집적도가 높기 때문에, 큰 메모리 칩에 사용된다.

- 상대적으로 느리다.

- SRAM

- 가격이 비싸다

- 매우 빠르다.

집적도 : 밀도, 단위 면적당 비트 개수

이 둘은 모두 휘발성 메모리이기에 전원이 끊어지면 데이터가 모두 사라진다.

참고

비휘발성 메모리에는 코어 메모리가 있다. 이는 오래된 기술이지만 비휘발성이라는 특정으로 인해 여전히 가치가 있다.

읽기 전용 메모리

읽기 전용 메모리(read-only memory, ROM)은 그리 정확한 이름은 아니다. 읽기만 가능한 메모리는 그닥 쓸모가 없다.

이러한 이유 때문에, 이름을 한 번만 쓸 수 있는 메모리(write-once memory)라 부르는게 좋아보인다.

블록 장치

메모리를 읽거나 쓰려면 시간이 걸린다. 밀가루가 필요할 때마다 매번 가게에서 밀가루를 사와야 한다고 생각해보자. 밀가루를 한 포대 사놓고 필요할 때마다 꺼내서 쓰는 방법이 더 효율적일 것이다. 큰 메모리 장치에서도 이러한 원리를 사용한다.

대량 저장장치(mass storage)로 알려진 디스크 드라이브(disk drive)는 엄청나게 많은 데이터를 저장하기에 좋은 장치이다. 중국집의 회전식탁에 원하는 음식을 손을 사용하여 가져온다. 디스크에서 디스크 헤더가 손 역할을 한다.

다른 유형 메모리에 비해 상대적으로 느리다. 회전식탁과 마찬가지로 내가 원하는 데이터를 놓치면 다시 한바퀴가 돌아 내 앞으로 음식이 올 때 까지 기다려야 한다.

디스크의 영역을 자화시켜서 데이터를 저장하기에 코어 메모리와 마찬가지로 비휘발성이다.

즉, 디스크 드라이브는 기록 밀도와 속도를 맞바꾼 기억장치이다.

플래시 메모리와 SSD

플래시 메모리는 가장 최근에 나타난 EEPROM 유형의 매체이다. DRAM과 마찬가지로 버킷에 전자를 담는 방식으로 작동하지만, 버킷이 DRAM보다 더 크고 잘만들어져 전자가 새진 안흔다.

디스크 드라이븐느 점차 SSD(Solid-state drive)로 대체되고 있다. 이는 디스크 드라이브 모양의 패키지에 넣은 플래시 메모리와 같다.

오류 감지와 정정

어떠한 이유로 인해 메모리의 비트가 잘못될 수 있다. 이런 일이 발생했을 때는 가능한 빨리 알아차리고 즉시 복구를 진행해야 될 것이다.

패리티(parity)를 사용하면 단 1비트만 데이터가 잘못된 경우를 감지할 수 있다. 전체 비트 시퀀스의 1의 개수가 짝수인지 홀수인지에 따라 다음 두 가지로 나뉜다.

- 짝수 패리티 : 모든 비트에 XOR을 취하는 방식을 통해 감지

- 홀수 패리티 : 모든 비트에 XOR 한 값의 보수를 사용하여 감지

이 방법은 끊임없이 변화하는 데이터를 처리할 때 유용하다. 이러한 경우 외에 정적인 데이터 블록을 검증하는 경우엔 체크섬이라는 더 싼 방법이 있다.

체크섬(checksum)은 데이터의 각 지점(예 : 바이트)을 n 비트값으로 더하고 n 비트를 넘어가는 값을 무시한다. 체크섬에서 사용하는 값(n)이 클수록 위양성 결과가 발생하기는 더 어려워진다.

순환 중복 검사(CRC, cyclic redundancy check)는 수학적으로 체크섬보다 더 나은 대체이다. 데이터의 고유성을 충분히 들어낼 수 있는 방식으로, 검증 숫자를 계산 후 데이터가 약간이라도 바뀌면 검증 숫자가 더 이상 일치하지 않게 바꾸는 방법이다.

출처) 한 권으로 읽는 컴퓨터 구조와 프로그래밍

http://www.yes24.com/Product/Goods/102266032