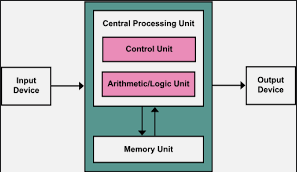

ALU

산술 논리 장치는 덧셈, 뺄셈같은 두 숫자의 산술 연산과 배타적 논리합, 논리곱, 논리합같은 논리연산을 계산하는 디지털 회로이다.

프로세서에서 명령어를 실행할 때 fetch, decode이후 execution단계에서 ALU가 연산을 수행한다. ALU에서는 이진수의 산술연산과 논리연산을 지원한다.

Addition and Subtraction

- 덧셈 : 두 이진수를 단순하게 더한다

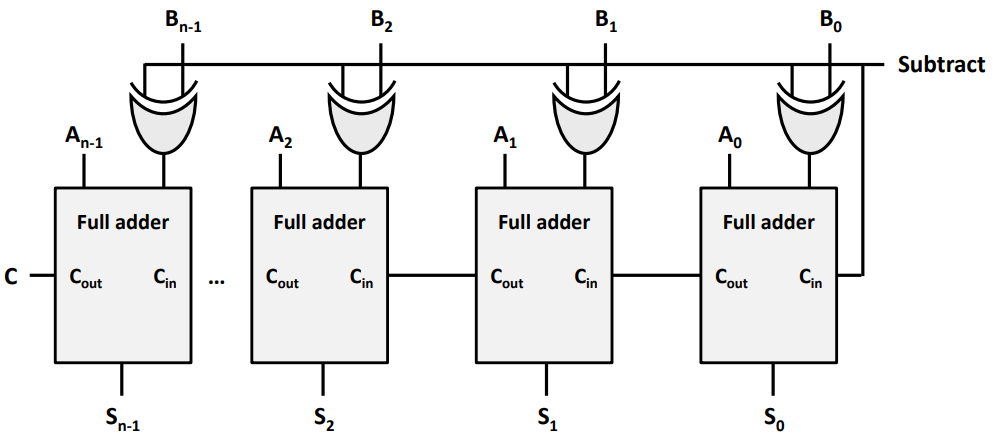

- 뺄셈 : 두번째 피연산자를 2의 보수를 취해 더한다

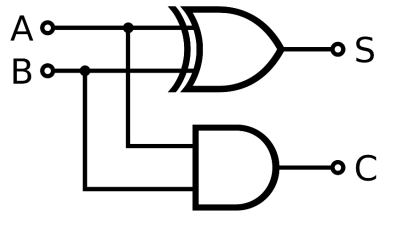

- Half Adder : 1-bit 이진수 덧셈

- Full Adder : carry를 포함한 1-bit 이진수 덧셈

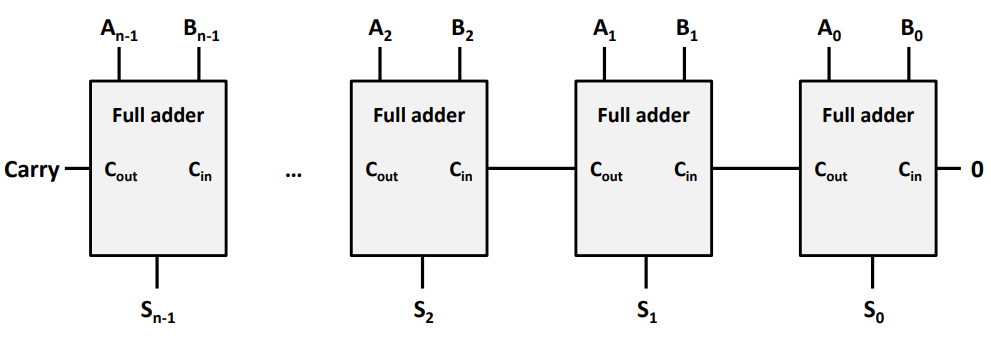

- N-bit parallel binary adder : n-bit 이진수 덧셈

- Adder with Subtractor : n-bit 이진수 덧셈 및 뺄셈

Overflow

- 계산결과가 너무 크거나 작아서 범위를 넘어가는 경우

- 부호가 같은 두 이진수를 더했을 때 다른 부호가 나오는 경우

- 양수에서 음수를 뺐을 때 음수가 나오는 경우

- 음수에서 양수를 뺐을 때 양수가 나오는 경우

- Detection : add, addi, sub를 사용하면 overflow가 발생할 때 exception handler로 jump함

- Ignore : addu, addui, subu를 사용하면 overflow를 무시함(unsigned)

Multiplication

-

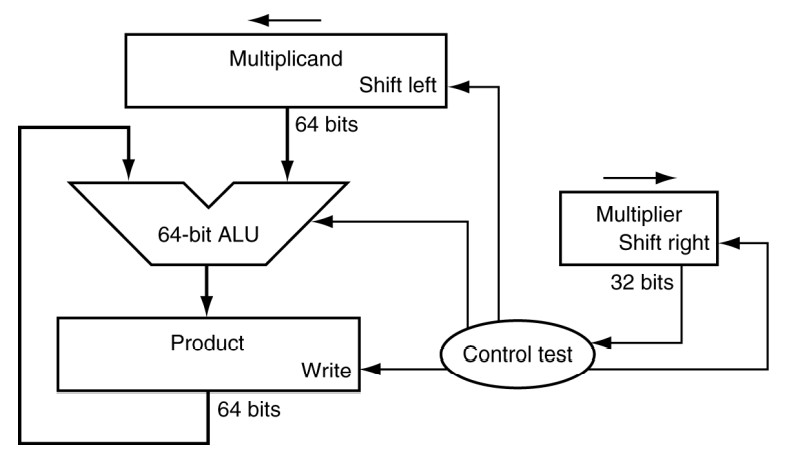

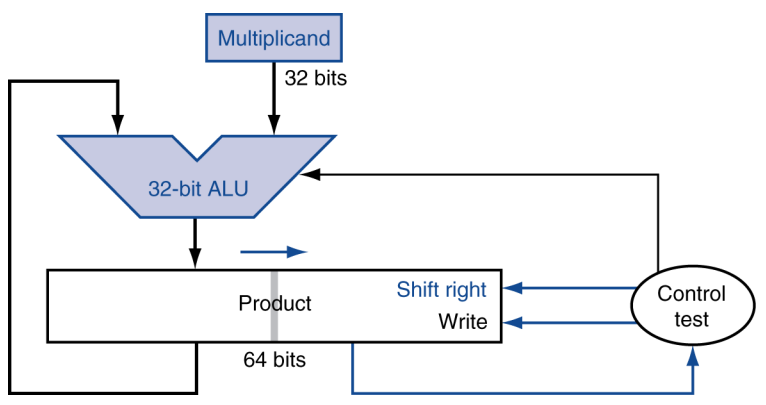

ver1 : 곱하는 수가 1이면 곱해지는 수를 해당 bit만큼 shift해서 더한다

- 문제점 : 연산과정이 지나치게 길고, multiplicand의 절반이 항상 0이며, 특정 반복횟수까지 낭비되는 공간이 있다

-

ver2 : 64-bit product register를 사용하여 multiplier와 product를 동시에 저장. product register를 오른쪽으로 shift하여 multiplier와 multiplicand를 동시에 이동하기 때문에 계산과정이 효율적이고, multiplicand 레지스터가 n-bit이기 때문에 공간의 낭비를 줄일 수 있다

- signed multiplication : 두 수의 부호를 모두 양수로 바꾼 후 계산한 뒤 부호를 계산한다

- faster multiplication : 여러개의 adder를 두어 연산을 병렬적으로 처리한다

Division

-

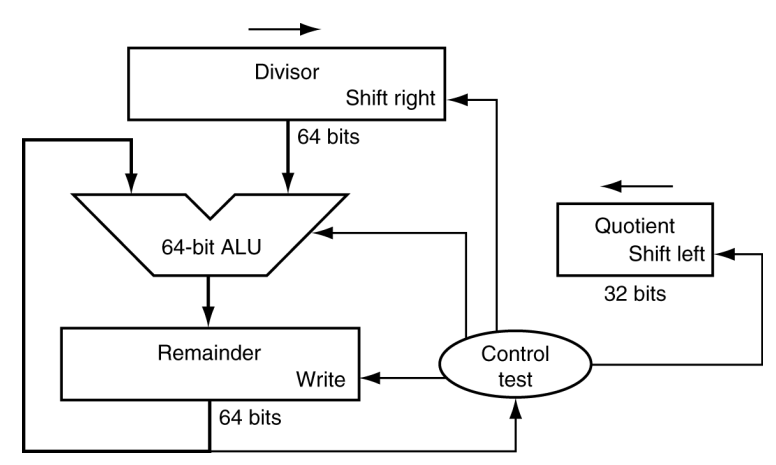

ver1 : 나누는 수를 왼쪽으로 shift하면서 뺄셈을 반복한다

- 문제점 : 곱셈과 동일하게 연산과정이 길고 공간이 낭비된다

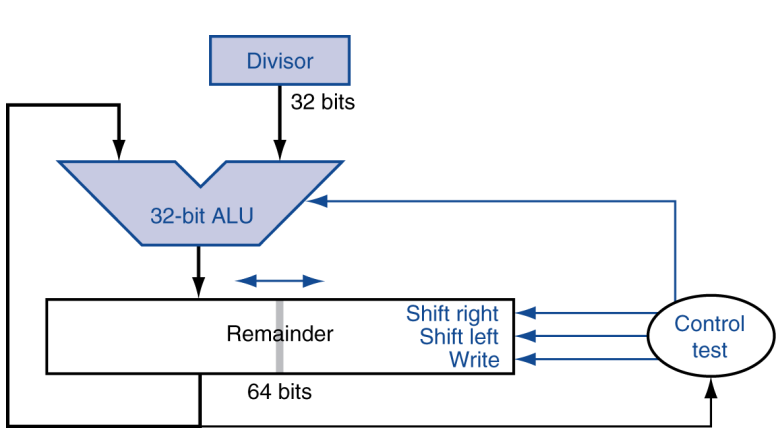

-

ver2 : 64-bit remainder register를 사용하여 deviend와 quotient를 동시에 저장.

-

signed division : 두 수를 양수로 바꾸어 계산한 뒤 부호를 결정한다