Overview of ARM Architecture & Cortex-M Processors

임베디드시스템설계

ARM Architecture

ARM은 RISC processor core design으로 가장 유명하다. ARM은 직접 공장을 소유해서 processor를 생산하는 것이 아니라 디자인과 라이센스를 주고 다른 회사에서 생산해서 파는 방식을 사용....

ARM architecture은 RISC architecture이다. fixed length instruction을 사용하고 load-store architecture이다(memory-to-register load instruction과 register-to-memory store instruction이 있고 arithmetic instruction으로 메모리 접근은 불가능하다).

ARM Cortex Processors

-

Cortex-Aseries (application)

full OS를 지원할 정도의 high performance를 가지고 있는 프로세서이다. high-end system에 사용한다. 성능이 좋지만 비싸다. -

Cortex-Rseries (real-time)

높은 성능을 가지고 있고 real-time application에서 사용할 수 있다. -

Cortex-Mseries (microcontroller)

비용에 민감한 상황에서 합리적으로 선택할 수 있는 마이크로 컨트롤러다. 센서같은 것도 들어있다. 비용이 저렴하지만 성능이 떨어진다.

ARM procesors & ARM architectures

ARM architecture은 instruction set을 포함한 여러 detail을 설명하는 것이고 architecture reference manual에 문서로 정리되어 있다.

ARM architecture에 기반한 physical implementation이 ARM processor이다. 구현과 관련한 detail이 더 많이 있다. 프로세서의 technical reference manual에 기술된다.

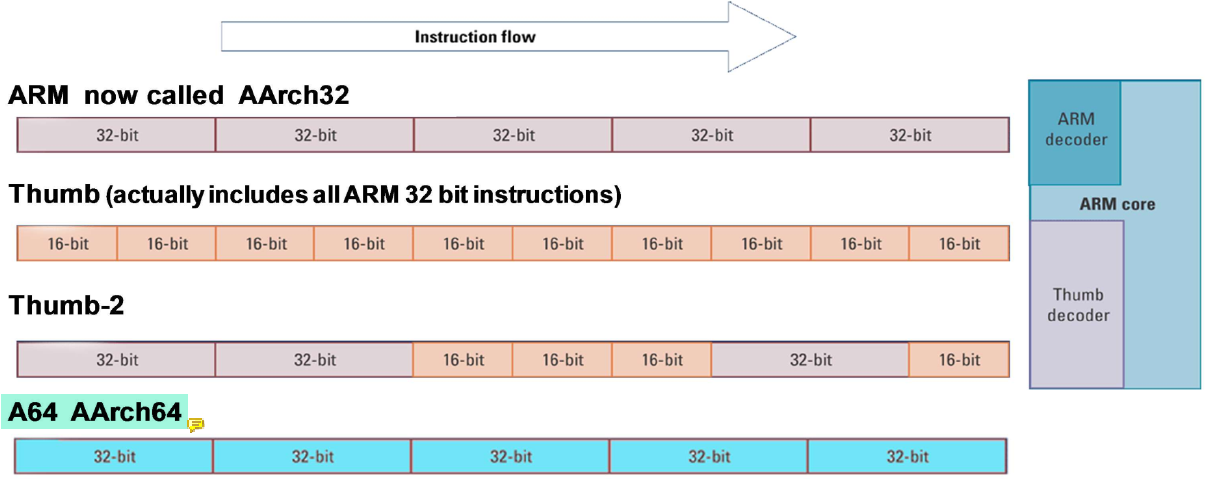

Instruction Sets

AArch64만 64bit을 위한 것이고 나머지 instruction은 32bit용이다.

AArch32는 instruction의 길이가 32bit이고 Thumb은 16bit이다. Thumb-2 32bit와 16bit를 모두 이용한다.

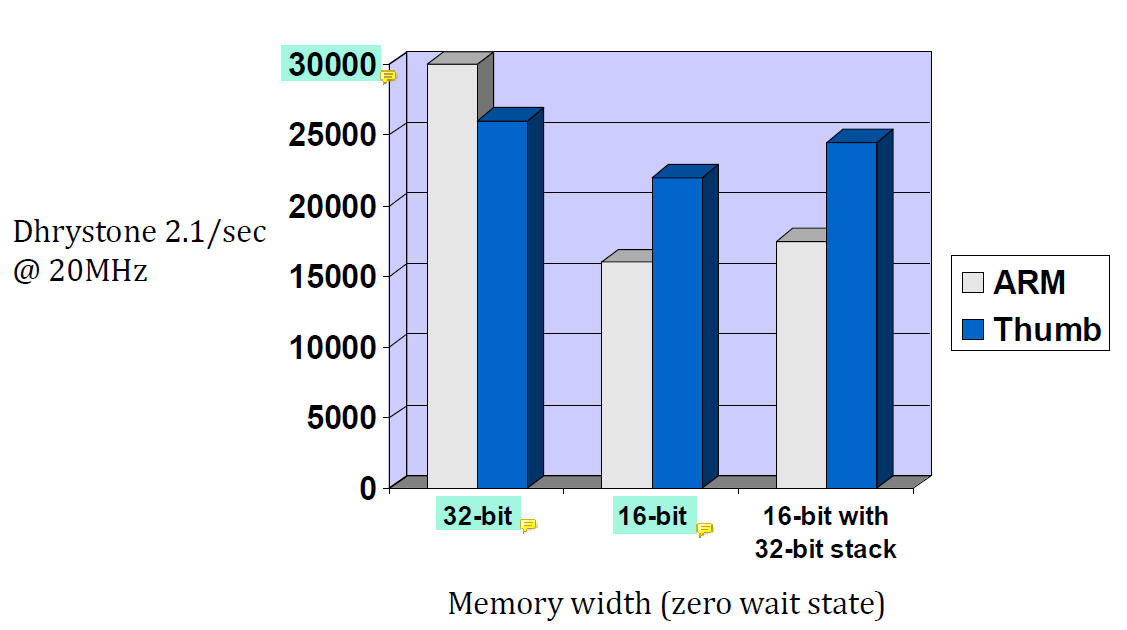

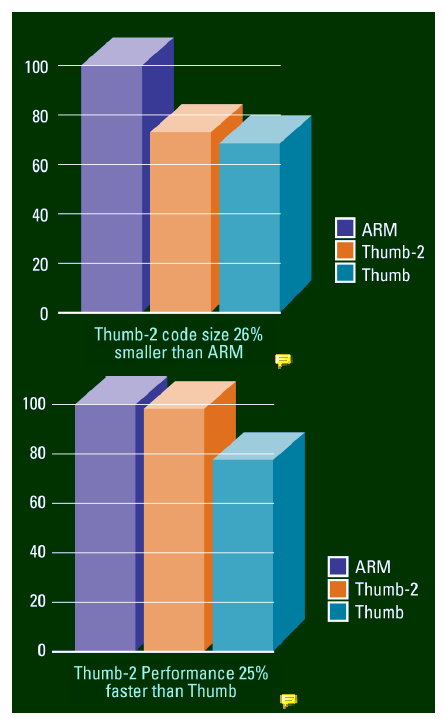

위의 그래프에서 세로축은 성능을 의미하며 higher is better이다.

위의 그래프에서 세로축은 성능을 의미하며 higher is better이다.

그래프를 분석해보자.

-

32bit인 경우 :

ARM이Thumb보다 성능이 좋다.

ARM이Thumb에 비해 total number of instruction을 줄일 수 있기 때문이다.

instruction의 bit수가 클 수록 한 instruction을 통해 할 수 있는 일이 많아진다. memory width가 32bit인데 굳이 16bit instruction을 사용하는 것은 비효율적이다. -

16bit인 경우 :

Thumb이ARM보다 성능이 좋다.

ARMinstuction은 32bit이기 때문에 memory width가 16bit일 때 사용하려면 한 instruction을 fetch하기 위해 memory access를 2번 해야한다. 그래서ARM의 속도가 더 느려지게 된다.

Thumb-2instruction은ARMinstruction과Thumbinstruction이 각각 32bit와 16bit의 fixed length를 쓰는 것과 다르게 32bit와 16bit를 둘 다 사용할 수 있다.

Thumb-2 instruction은 ARM instruction을 사용하는 것에 비해 core size를 26% 줄일 수 있다. 또한 complex instruction은 32bit으로 나타낼 수 있기 때문에 Thumb instruction에 비해 25% 성능이 더 좋다.

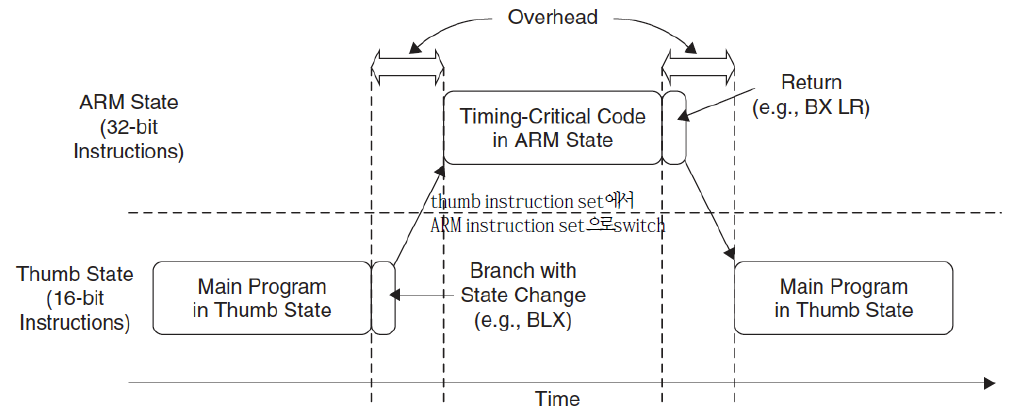

Instruction State Switch

ARM state에서는 32bit instruction을 사용할 수 있고 Thumb state에서는 16bit instruction을 사용할 수 있다.

current instruction state는 branch address의 LSB를 통해 결정된다.

LSB가 0인 경우 : ARM mode

LSB가 1인 경우 : Thumb mode

Cortex-M Processor Family

M뒤에 붙은 숫자가 작을 수록 작은 프로세서이다.

-

Cortex-M0: 매우 작은 프로세서.. 싸고 성능 안좋음 -

Cortex-M0+: 가장 energy-efficient한 프로세서. small embedded system에 사용한다. -

Cortex-M1: FPGA 디자인에 최적화 되어있는 프로세서. -

Cortex-M3: low-power microcontroller를 위한 작고 powerful한 embedded 프로세서.

ARM instruction을 알아들을 수 없고 Thumb과 Thumb-2 instruction만 decode할 수 있다. harvard architecture를 사용한다.

3-stage pipeline을 사용한다. -

Cortex-M4:Cortex-M3에서 multimedia를 위한 instruction이 추가된 프로세서. -

Cortex-M7: high-performance 프로세서. -

Cortex-M23:Cortex-M0+와 비슷하지만Cortex-M0+이Armv6-Marchitecture를 사용하는 것과 달리Armv8-M을 사용한다. TrustZone security extension을 지원한다! -

Cortex-M33:Cortex-M3,Cortex-M4와 비슷하며 TrustZone security extension을 지원한다.

Cortex Programmer's Model

-

Fully programmable in C :

Cortex-M은 C로 fully programmable하다. 즉, C로 펌웨어를 만들 수 있다. -

Stack-based exception model : 하드웨어에서 exception이 발생하면 handle하기 전에 stack에 자동으로 register값이 push되고 handle이 끝나면 그 값들을 restore한다.

-

Thumb & Thumb-2 instruction sets : ARM instruction은 사용하지 않는다.

-

Two processor modes : user task를 위한 thread mode와 exception을 위한 handler mode가 있다.

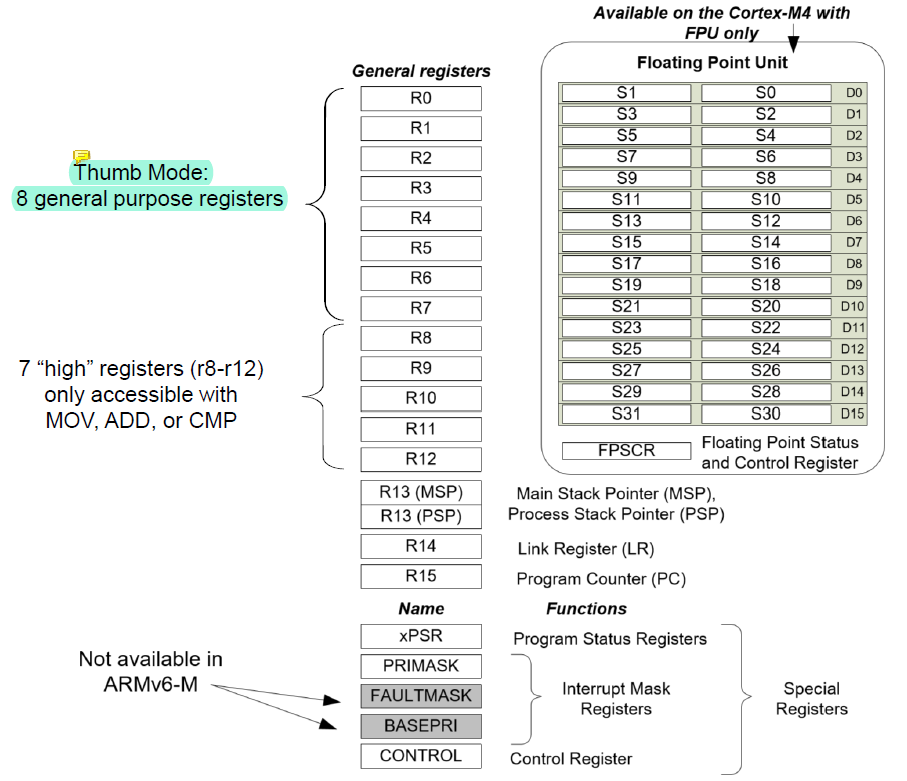

Cortex-M 프로세서에는 R0부터 R12까지 13개의 레지스터가 있지만 Thumb mode에서는 R0부터 R7까지 8개의 레지스터밖에 사용하지 못한다.

그것은 Thumb instruction의 크기가 너무 작아서 그렇다. 16bit밖에 사용하지 못하는데 13개의 레지스터를 사용하려면 레지스터의 위치를 표현하는 데에 4bit를 써야한다. 8개의 레지스터만 쓰면 위치를 나타낼 때 3bit면 충분하므로 Thumb mode에서는 사용할 수 있는 레지스터의 수를 제한한다.

Stack Pointers

R13은 stack pointer로 사용된다.

Cortex-M에는 총 2개의 mode가 있기 때문에 stack pointer도 2개가 있다.

- Main stack Pointer(

MSP) : default stack pointer이다. OS kernel과 exception handler, privileged mode에서 사용된다. 일반적인 운영체제로 생각해보면 kernel mode에서 사용되는 stack pointer를 의미한다. - Process Stack Pointer(

PSP) : user application code에서 사용하는 stack pointer를 의미한다.

두 stack pointer는 한 번에 하나만 visible하다. 각 시점에서 R13을 통해 현재 사용중인 stack pointer만 지정할 수 있다.

예를 들면 MSP를 사용중일 때는 R13을 통해 MSP만 보이며 PSP는 지정할 수 없다.

Link Register

R14는 link register이다(LR).

LR은 function이 call됐을 때 return address를 저장하는 용도로 사용된다.

main:

...

BL foo ;PC = foo, LR = next instruction

...

foo:

...

BX LR ;ReturnProgram Counter

R15는 program counter이다(PC). PC에는 next instruction의 주소가 담겨있다.

PC를 읽어들일 때 LSB는 항상 0이다.

PC에 write를 할 때 branch가 유발된다. LSB는 Thumb state operation을 의미하기 위해 항상 1이어야 한다. 만약 0이라면 Cortex-M에서는 fault exception을 유발한다.

Special Registers

Cortex-M에는 special register가 있다.

- Program Status Registers (

PSRs) - Interrupt Mask Registers (

PRIMASK,FAULTMASK,BASEPRI) - Control Register (

CONTROL)

special register들은 MSR이나 MRS instruction을 통해서만 접근할 수 있다.

MSR이나 MRS은 memory address를 통해서 access하지 않고 register를 통해서만 access한다!

MRS <reg>, <special_reg> ; Read special register

MSR <special_reg>, <reg> ; Write to special registerProgram Status Registers (PSRs)

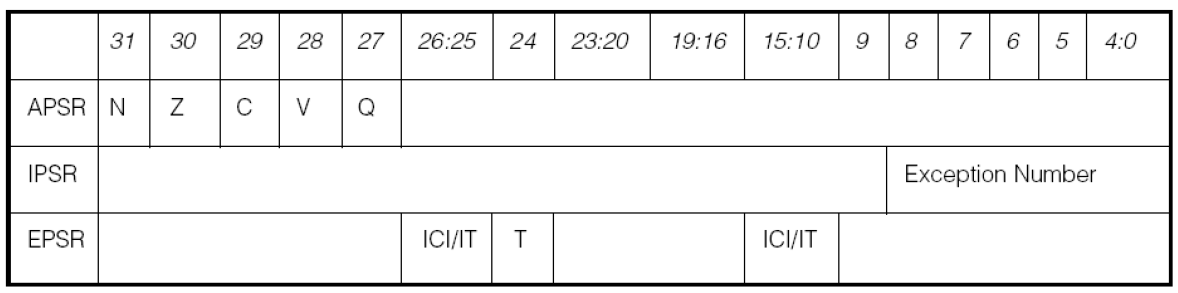

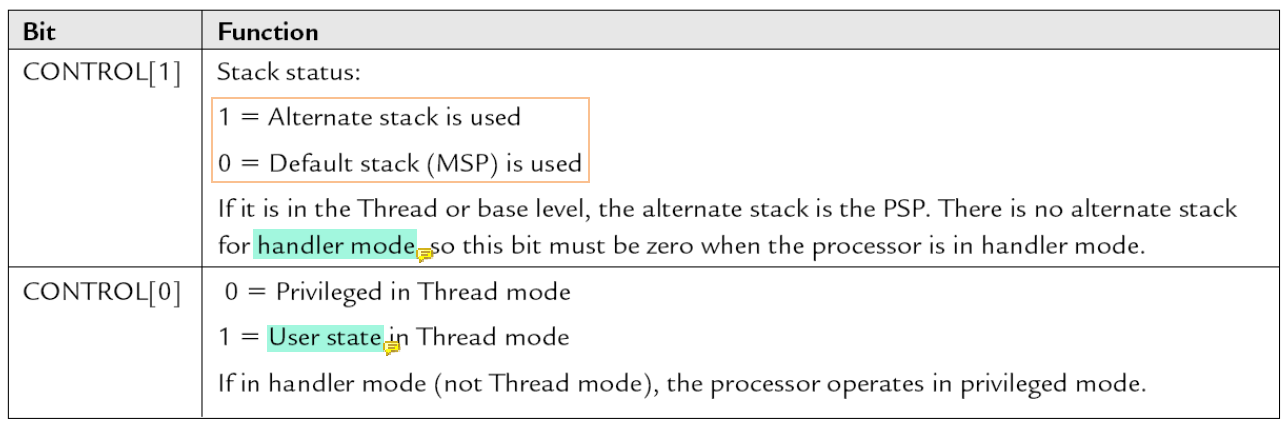

PSRs은 3개의 status register로 나누어진다.

- Application PSR (

APSR) - Interrupt PSR (

IPSR) - Execution PSR (

EPSR)

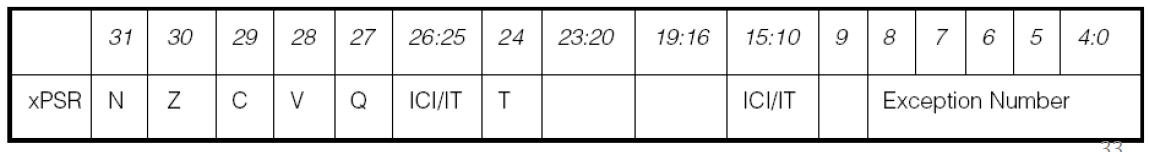

만약 다 합쳐서 collective item으로 접근한다면 xPSR이 사용된다(code에서는 PSR이 사용된다).

IPSR와 EPSR은 read-only이다.

MRS r0, APSR ; Read flag state into r0

MRS r0, IPSR ; Read exception/interrupt state

MRS r0, EPSR ; Read exception state

MSR APSR, r0 ; Write flag statexPSR에는 다음과 같은 방법으로 접근할 수 있다.

MRS r0, PSR ; Read the combined program status word

MSR PSR, r0 ; Write combined program state wordCortex-M의 bit field는 다음과 같다.

N, Z, C, V, Q는 APSR에서 사용하는 bit field이자 flag이다.

ICI/IT와 T는 EPSR에서 사용한다. T가 항상 1이라는 점에 주목하자.

Exception Number은 IPSR에서 사용한다.

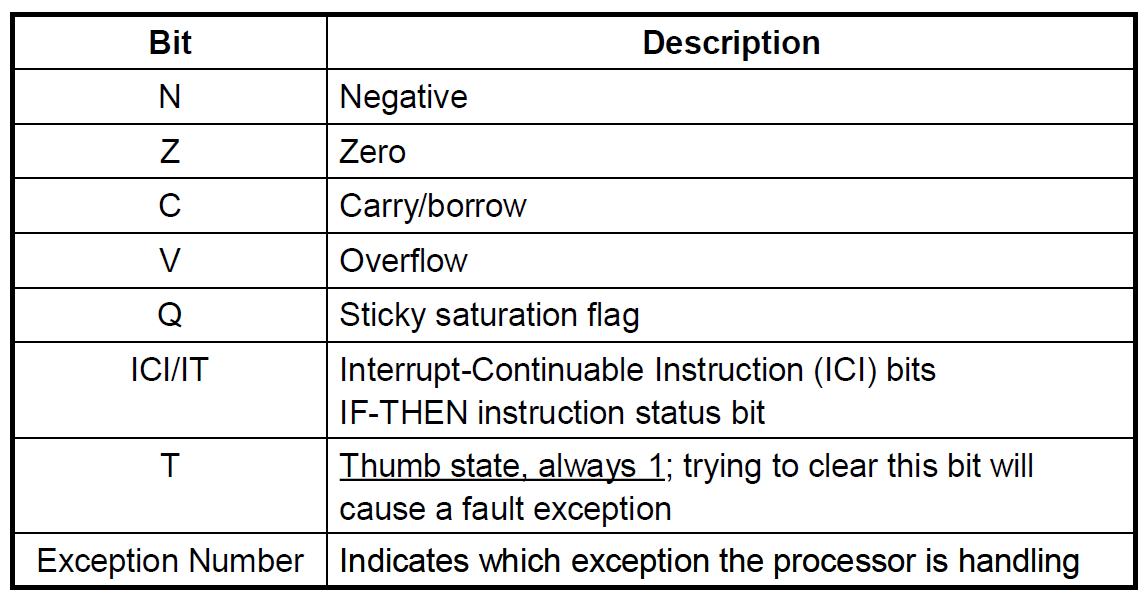

PRIMASK, FAULTMASK, BASEPRI

이 레지스터들은 exception을 disable할 때 사용된다.

PRIMASK, FAULTMASK, BASEPRI에 access하기 위해서는 MRS와 MSR instruction을 사용해야 한다.

세 레지스터는 user access level에서 set 될 수 없다.

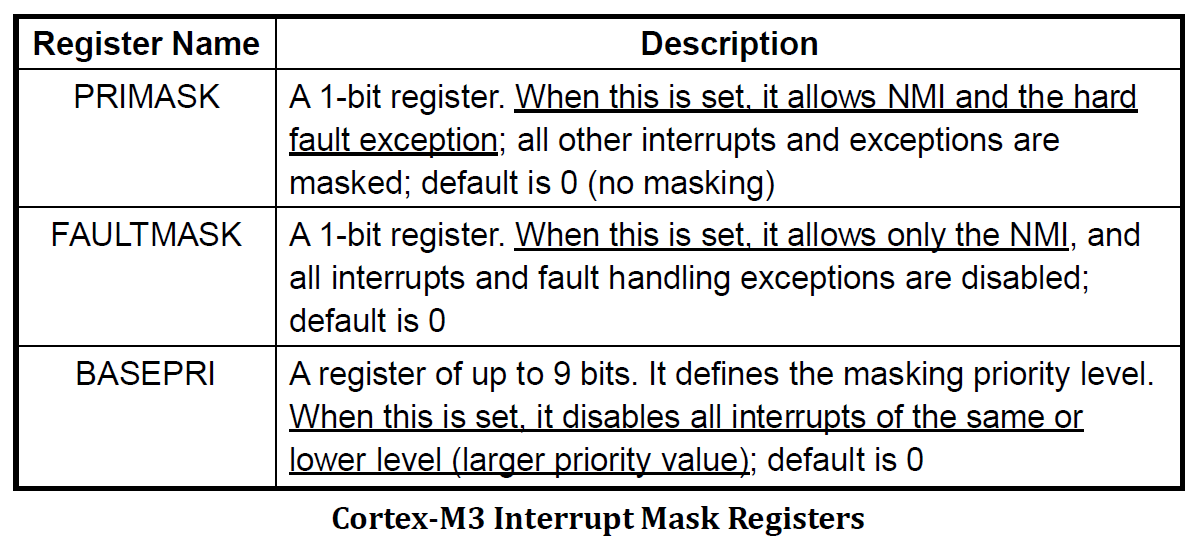

Control Register

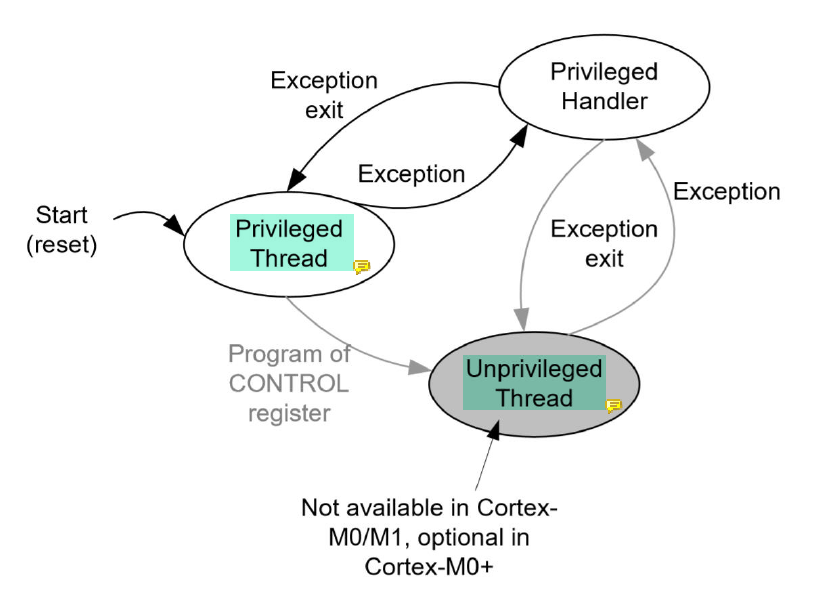

control register는 privilege level과 stack pointer selection을 정의하기 위해 사용된다.

CONTROL[1]은 Cortex-M3에서 handler mode일 때 항상 0이지만 thread mode에서는 0 또는 1 둘 다 될 수 있다. core가 thread mode이고 privilege mode일 때만 이 bit을 write 할 수 있다.

CONTROL[0]은 privilege mode에서만 write할 수 있다.

Control register에 access하기 위해서는 MRS와 MSR instruction을 사용해야 한다.

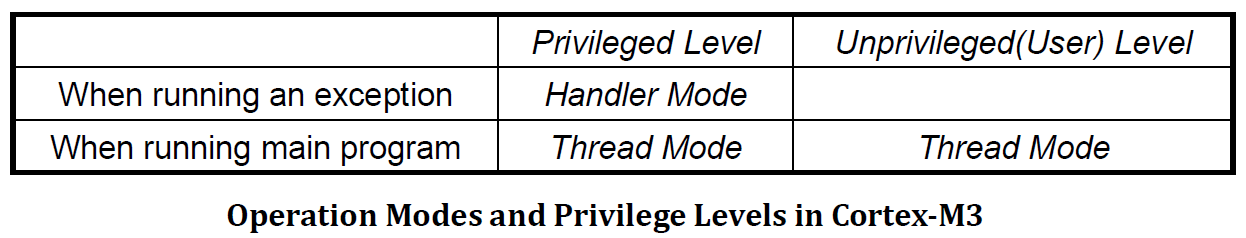

Operation Mode

두 개의 mode와 두 개의 privilege level이 있다. operation mode는 processor가 normal program을 running하고 있는지 exception handler를 running하고 있는지 나타낸다.

Processor Mode

- Handler mode : exception을 handle하기 위해 사용된다. 프로세서는 exception processing이 끝나면 thread mode로 return한다. handler mode에서 소프트웨어 execution은 항상 privileged이다.

- Thread mode : application software를 실행하기 위해 사용된다. 프로세서는 reset되면 thread mode에 enter한다. thread mode에서

CONTROLregister는 software 실행이 privileged인지 unprivileged인지 나타낸다.

Privilege Levels

- Unprivileged (User) : software는

MSR(move register to special register),MRS(move special register to register) instruction에 limited access를 하고CPS(change processor state) instruction을 사용할 수 없다. - Privileged : software는 모든 instruction을 사용할 수 있고 모든 자원에 접근할 수 있다.

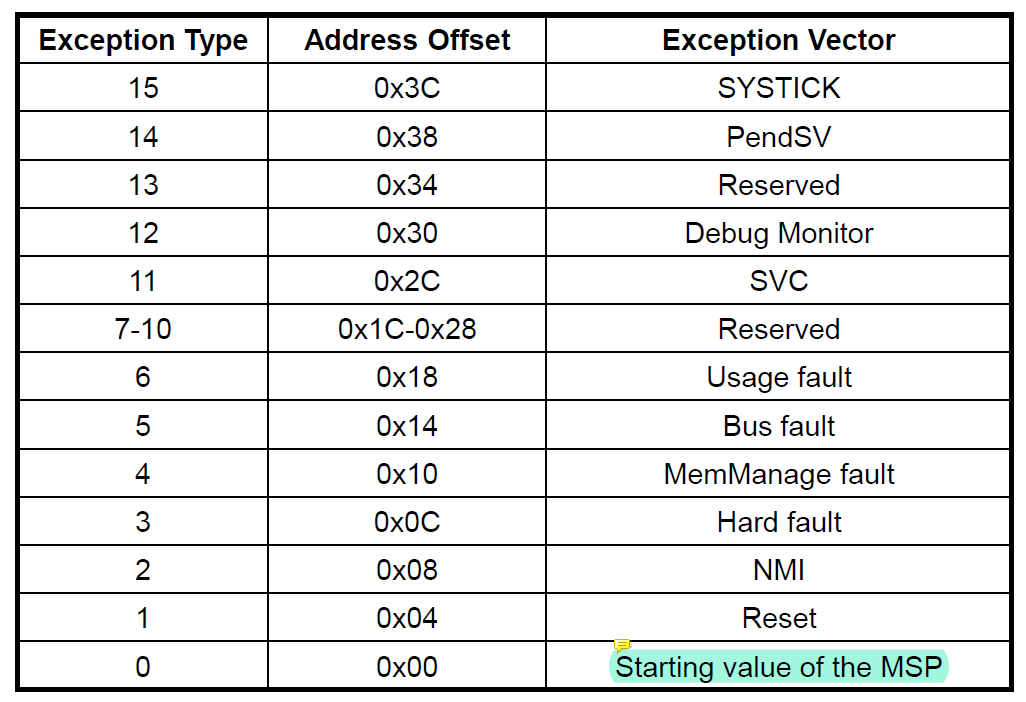

Vector Table

vector table은 word data의 array인데 각 data는 한 exception/interrupt의 handler의 starting address를 나타낸다.

vector table의 base address는 NVIC의 relocation register를 set해서 바꿀 수 있지만 초기값은 0x0이다.

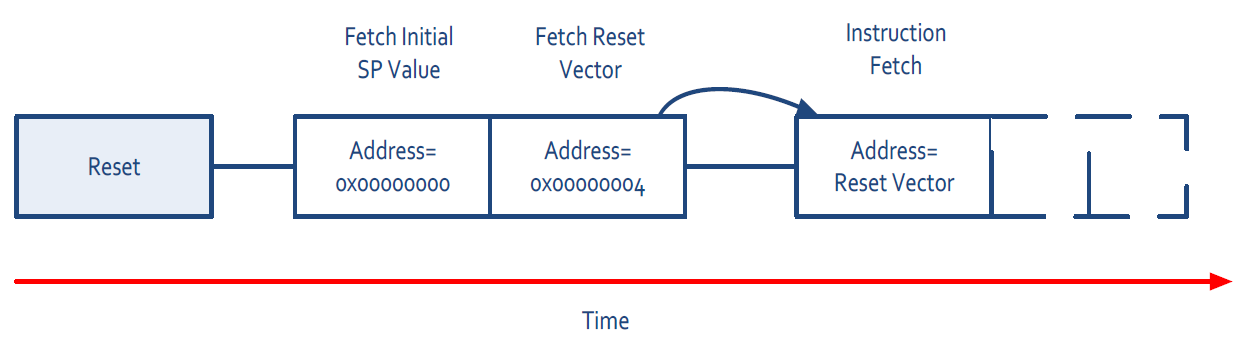

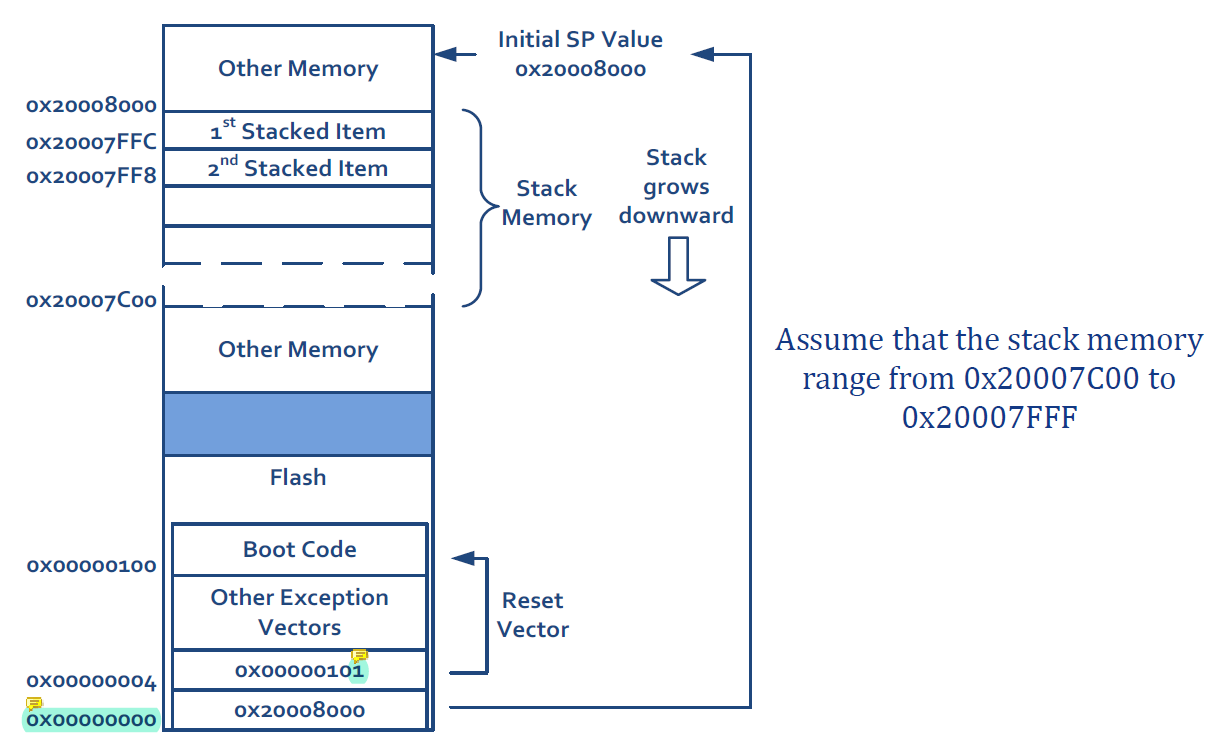

Reset Sequence

프로세서가 reset에서 exit하면 두 word를 memory로부터 읽는다.

0x00000000:R13의 default value (MSP)0x00000004: reset vector (startup program의 starting address, thumb state를 나타내기 위해LSB는 1로 set되어야 함)