클럭이란

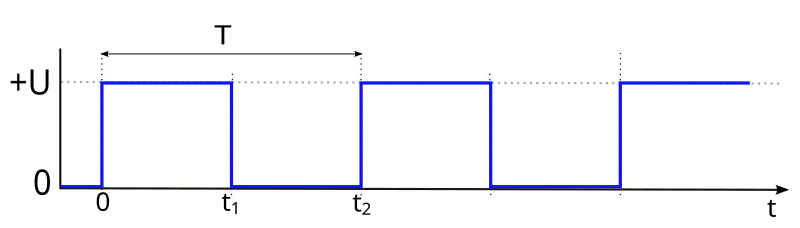

- 논리상태 H(high, 논리 1)와 L(low, 논리 0)이 주기적으로 나타나는 방형파(square wave) 신호

- 방형파: 장방형(직사각형)모양의 파

- 많은 경우 전자공학의 디지털 회로에서 클럭 신호에 맞추어 신호의 처리를 하는 동기처를 위해 사용한다.

- 클럭은 순차회로(sequential circuit)의 플립플롭(flip-flop)에서 반드시 필요하다.

- 컴퓨터는 수행되는 모든 연산의 타이밍을 맞추기 위해 펄스를 출력하는데 이것을 시스템 클럭이라고 한다.

- 즉, 컴퓨터의 모든 부품을 일사분란하게 움직일 수 있게 하는 시간 단위.

- 클럭의 "똑-딱-똑-딱" 주기에 맞춰 레지스터 간 데이터 이동이나, ALU에서 연산의 수행, CPU가 메모리에 저장된 명령어를 읽어 들이는 등의 작업이 수행된다.

- 컴퓨터는 한번 신호를 보낼 때마다 한번씩 동작을 하므로 클럭수가 높을수록 같은 시간에 더 많은 일을 할 수 있다.

클럭 신호의 요소

- 신호의 크기

- 주기를 결정하는 주파수

- 한 주기 동안 상태 H와 L의 시간인 듀티비

1. 신호의 크기

클럭 신호는 디지털회로에서 많이 사용하므로 신호의 크기는 전압으로 나타난다.

디지털회로에서 전압은 보통 논리 게이트의 전압과 같게 설계한다.

전압상태의 기준은 0V(ground)을 L 상태로 Vcc을 H상태로 발생 시키는 것이 보통이다.

H는 5V, 3.3V 등 논리 게이트에 따라 다르고 처음 칩 설계 시 고정되어 있다.

초기에 5V를 많이 사용하였으나 3.3V 등으로 낮아지는 경향이 있다.

2. 주파수

디지털 회로 설계 요구사항에 따라 결정하는 것이 일반적이다.

규모가 있는 디지털 회로는 보통 다양한 주파수가 필요한 경우가 발생하는데, 내부의 카운터 회로에 의해 주파수 변환하여 사용한다.

따라서 필요한 가장 빠른 주파수 를 수정발진기(crystal oscillator) 를 사용하여 만들고 이것으로 분배한다.

수정 발진기의 발진 주파수보다 빠른 경우 위상동기회로(PLL) 방식의 회로 구성을 통해 칩 내부에서 높은 주파수를 발진하여 사용한다.

3. 듀티비

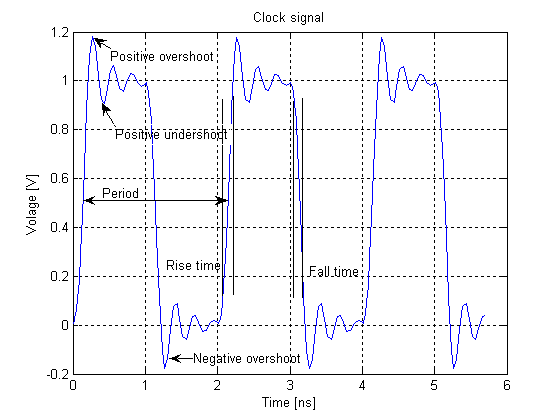

클럭 신호에서 한 주기 동안 H와 L의 시간차비인 듀티비가 보통 50%인 방형파를 많이 사용한다. 디지털 회로에서 신호가 반영하는 시점은, 신호의 상태 변화할 때의 짧은 순간에 이루어지는 경우가 많다. 상태 L에서 H로 변화하는 순간인 상승 에지(rising edge)나 H에서 L로 변하는 하강에지(falling edge)에서 동작하는 경우가 많다.

플립플럽은 상승 또는 하강에지에서 입력이 출력에 반영된다. 보통 마이크로프로세서에서는 듀티비가 50%을 많이 사용하지만, 경우에 따라 50%가 아닌 경우도 있다.

클럭은 두 개 이상의 디지털 회로의 동작을 통합하는 데에 쓰이는 신호이다.

동기화를 위해 클록 신호를 사용하는 회로는 갑자기 오르는 부분, 갑자기 떨어지는 부분에서 활발할 수 있다.

클럭 신호 발진

발진: 전기적 진동을 만들어내는 행위

디지털 회로에 사용하는 클럭의 발생은 수정발진기(quartz crystal oscilator)에 의해 만들어지는 경우가 대부분이다. 수정 발진자는 수정을 가공하여 박편 을 만들어 양극에 특정 정해진 주파수를 입력하면 자기의 고유 주파수만을 걸러내어 고유의 주파수를 발생시키는 소자이다. 입력된 주파수를 자기의 공진 주파수가 되도록 유도하는 방식으로 클럭이 발생한다.

- 박편: 얇은 조각

- 공진: 진동계가 그 고유진동수와 같은 진동수를 가진 외력(外力)을 주기적으로 받을 때 진폭이 뚜렷하게 증가하는 현상.

수정 발진기 자체에 직류 진압을 인가하면, 클럭 신호가 발생되지 않는다. 따라서 정해진 발진기의 주파수 근처의 방형파를 만드는 전자회로를 이용하여 수정 발진기에 신호를 인가하면 수정 빌진기는 자기 고유의 주파수만 공진 시켜 전자회로가 해당 주파수로 공진하도록 하는 유도 역할을 한다. 결국 전자회로와 결합하여 발진회로가 완성된다.

클럭 신호를 발진하면 이상적인 방형파가 불가능하다. 상승 또는 하강 엣지에서 상태 변화 시간이 필요하다.

클럭속도 (clock rate, 클럭 주파수)

- 컴퓨터 프로세서의 동작 속도

- 프로세서: 데이터를 처리하는 모든 종류의 처리 장치. CPU, GPU, DSP 등

- CPU는 프로세서의 한 종류이지만, 대부분의 경우 프로세서라 하면 CPU를 의미한다.

- 프로세서: 데이터를 처리하는 모든 종류의 처리 장치. CPU, GPU, DSP 등

- 일반적으로 프로세서의 클럭생성기가 부품의 작동을 동기화하는데 사용되는 펄스를 생성할 수 있는 주파수를 나타내며, 프로세서 속도의 지표로 사용된다.

- "초당 주기"로 측정하며, 헤르츠(Hz) 단위를 사용

- 헤르츠(Hz): 1초에 한 번.

- 실제 CPU의 기본 속도는 2.5GHz, 최대 속도는 4.9GHz.

- 1초에 클럭이 기본적으로 25억 (2.5 * 10^9)번,

- 순간적으로 최대 49억(4.9 * 10^9)번 반복됨을 의미

클럭 속도는 일정하지 않다.

CPU는 기본 클럭 속도(Base)와 최대 클럭 속도(Max)로 나뉘어 있다. 이처럼 cpu는 계속 일정한 클럭 속도를 유지하기보다는 유연하게 속도를 조절한다. 최대 클럭 속도를 강제로 더 끌어올릴 수도 있는데, 이런 기법을 오버클럭킹(overclocking) 이라고 한다.

클럭 속도가 반드시 컴퓨터의 속도를 좌우하는 것은 아니다.

자세히 말하면 컴퓨터의 성능을 측정하는 경우 CPU의 클럭 속도가 중요하지만 다른 하드웨어/소프트웨어의 구성에 의해 더 크게 영향을 받는다. 이를테면 프론트 사이드 버스의 속도, 램의 클럭, CPU 버스, L1/L2/L3 캐시의 양에 따라 컴퓨터 속도는 다르게 나타날 수 있다. 좀 더 정확한 평가를 위해 벤치마크를 사용한다.