1. From CPU to OS

1. 부팅 시나리오

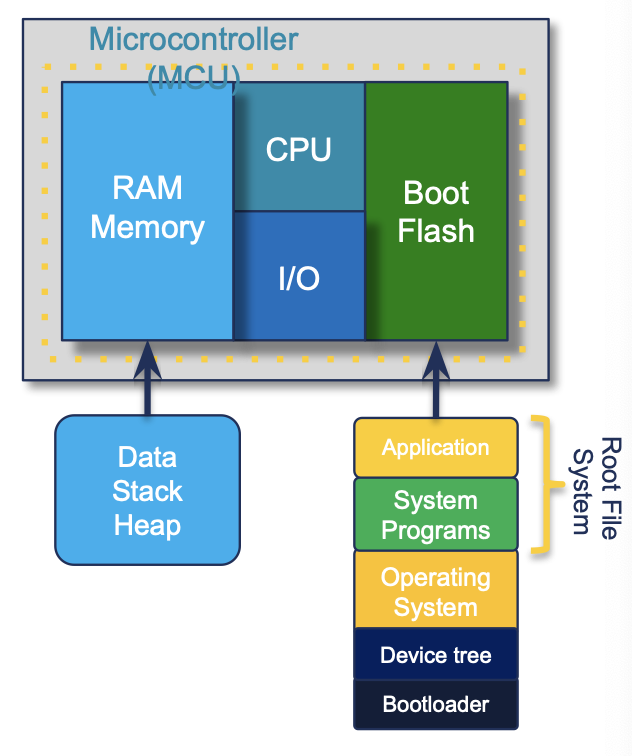

1. Micro Controllers(MCU)

- 모든 소프트웨어는 (Bootloader + device + tree + OS + root file system) 마이크로 컨트롤러에 내장된 저장장치(boot flash)에 저장되어 있음

- 모든 소프트웨어는 persistent storage에서 수행

- CPU reset Vector는 boot flash에 있음

- RAM은 마이크로 컨트롤러에 내장되어 있고, data, stack, heap으로만 사용

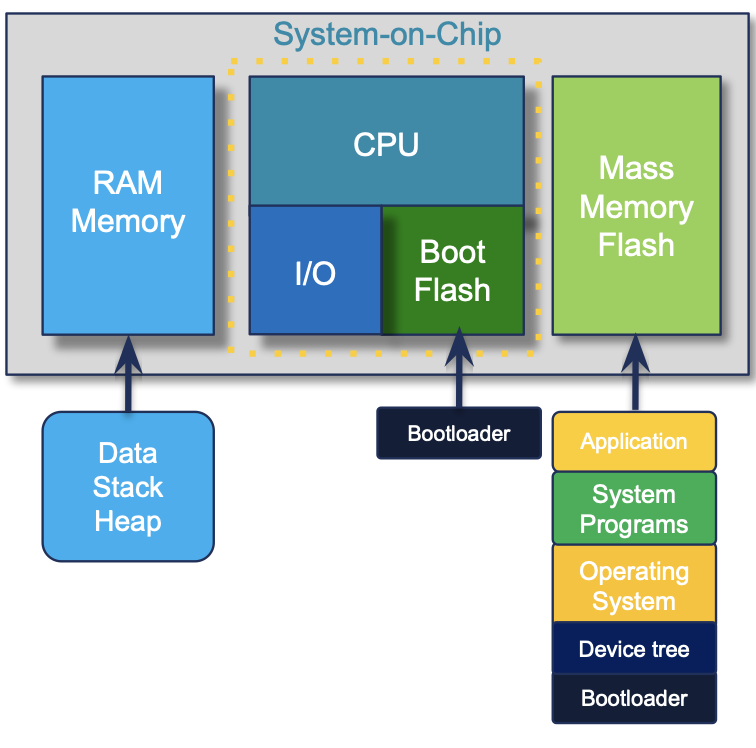

2. SoC(System-on-chip)

- bootloader 는 boot flash에 저장됨

- CPU Reset Vector는 boot flash에 저장됨

- root filesystem, OS, device tree는 mass memory flash에 저장되고, bootloader에 의해 RAM에 적재됨

- RAM은 SoC 외부에 있고, operating system + application software,root filesystem(RAM disk), data stack, heap 이 올라감

2. SoC에서 CPU to OS 과정

1. Power UP

- CPU 실행

- CPU는 Boot Flash의 0x0000_0000 저장된 CPU reset vector를 통해 bootloader 의 첫번째 instruction으로 jump

- bootloader software를 boot flash에서 수행

2. during bootstrap

- bootloader software 수행

- CPU의 RAM memory controller 수행

- Stack 과 heap을 RAM에 mapping하기 위해 register 값 설정

- device tree, OS, system program, application을 RAM으로 복사

3. end of bootstrap

- OS의 첫 명령어로 jump

- CPU는 이제부터 OS를 실행

- OS는 응용프로그램을 위한 수행 환경 설정

- OS는 응용프로그램 시작

2. Device tree

1. 커널이 하드웨어 자원의 명세를 확인하는 두가지 방법

- 하드웨어 자원: I/O devices, memory, ...

- 커널 바이너리 코드에 Hardcode 하는 방법

-> 하드웨어가 변경되면 소스코드를 변경하여 재컴파일해야 하는 번거로움- bootloader가 커널 바이너리를 로드할 떄 자원 명세 파일(device tree blob)을 가져오는 방법

2. DTS(Device Tree Source) -> (컴파일) -> DTB(Device Tree Blob)

- 하드웨어 변경 시 DTS 컴파일만 하면 됨

- 커널 재컴파일이 필요 없어 시간 절약

- 컴파일러(Device Tree Compiler) source code는 scripts/dtc에 있음

1. DTS 파일

- ARM arch에서 dts 파일은 아래의 위치에 존재

-> arch/arm64/boot/dts- device tree compiler로 DTS를 DTB로 컴파일

-> DTB는 부트로더에서 로드되고, 커널이 boot time에 parsing- Device tree file은 dtsi와 같은 여러 파일로 나누어 질 수 있음, 이러한 경우 dts 파일이 하위 dtsi 파일을 통합

3. Exception Handling

1. Synchronous exceptions

- 현재 수행중인 instruction에 의해 발생하거나 또는 이와 관련 있는 exception

- invalid instruction: UNDEFINED exception

- TRAP: OS나 hypervisor 같은 상위 entity에서 하위 EL의 수행을 가로챔

- Memory access: previleged(특권) 영역을 접근하거나 read-only 영역에 write 할때 등등

- Exception-generating instruction

-> SVC: EL0->EL1

-> HVC: EL1->EL2

-> SMC: EL1->EL3 OR EL2->EL3- Debug exception: 디버깅용

2. Asynchronous exceptions

- 외부적인 요인으로 발생하여 현재 수행중인 instructions와 비동기적

- 외부 interrupt

- SError(System error): ABORT(중단) exception

- IRQ, FIQ

- Virtual interrupt: vIRQ, vFIQ, vSError

4. 가상 메모리

1. 가상 메모리의 이점

- OS는 메모리의 여러 조각난 물리적 영역을 애플리케이션에 단일 연속 가상 주소 공간으로 제시할 수 있음

- 소프트웨어 개발자들이 물리적 메모리에 대해 걱정할 필요가 없게 해줌

2. OS의 역할

- 각 애플리케이션은 물리적 시스템의 다른 위치에 매핑될 자체 가상 주소 세트를 사용할 수 있음

- OS는 다른 응용 프로그램 간에 전환하여 지도를 다시 프로그래밍함

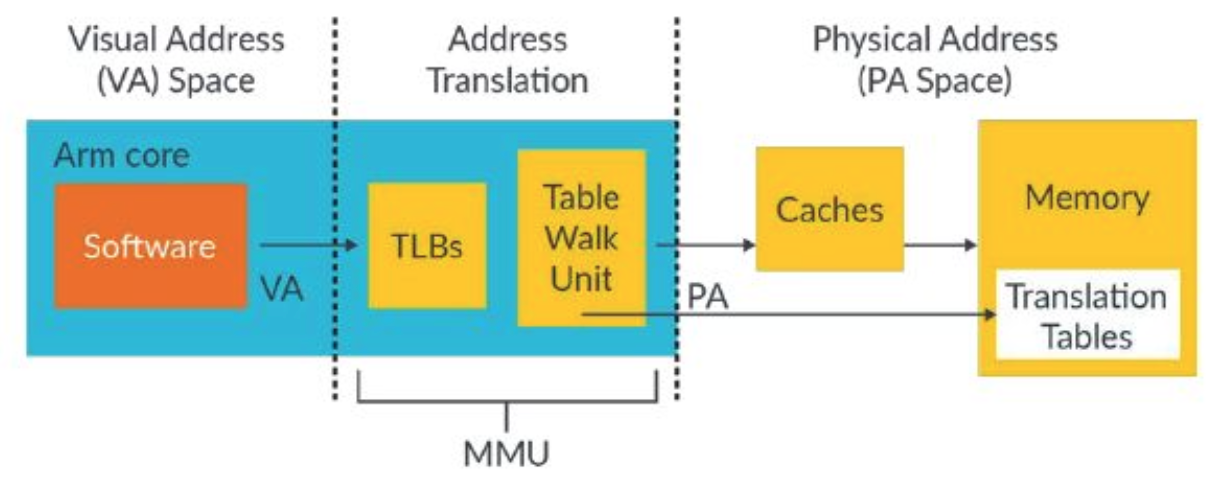

3. MMU

1. MMU(Memory Management Unit)이란?

- 가상 메모리를 물리 메모리 주소로 바꾸는데 하드웨어적으로 도움을 주는 유닛

- 메모리 액세스가 발생하기 전에 가상 주소를 물리적 주소로 변환해야 함

포함하고 있는 정보

- 테이블 워크 유닛: 메모리에서 번역 테이블을 읽는 로직

- 번역 룩사이드 버퍼 (TLB) : 최근에 사용된 번역 캐시

2. Cache에서도 메모리 변환 필요

- ArmV6 이후 CPU는 Physical address를 사용하여 data cache 저장

3. Table Entry

- translation 테이블은 가상 주소 공간을 같은 크기의 블록으로 나눔

- 블록당 테이블에 하나의 항목을 제공함으로써 작동합니다.