RAM(Random Access Memory)

실행중인 프로그램을 저장하는 메모리로 주기억장치라고도 불리며, 휘발성이다. RAM은 코드와 데이터를 저장하고 있는데 이들은 주소를 가지기 때문에, 주소를 통해 데이터에 접근이 가능하다.

RAM은 크게 SRAM과 DRAM으로 나뉜다. SRAM은 1비트당 트랜지스터 4개를 가지는데, Flip-Flop방식을 이용하기 때문에 Refresh를 하지 않아도 내용 변경이 일어나지 않아 속도가 빠릅니다. 따라서 보통 CPU의 L2, L3 cache에서 사용됩니다. 반면에 DRAM은 지속적으로 전류를 주지 않으면 내용이 변경되기 때문에 Refresh과정이 필요하고, 1비트 당 1개의 트랜지스터를 가지지만, 용량이 크고 싸다.

CPU(Central Processing Unit)

메모리에 적재되어 있는 데이터를 순차적으로 실행시키는데 클럭 신호에 맞춰 동작한다.

CPU는 크게 3가지의 구성요소를 가집니다.

1. 연산장치(ALU, Arithmatic Logic Unit)

레지스터에 저장된 데이터를 통해 산술, 논리 연산을 수행한다.

2. 제어장치(CU, Control Unit)

하드웨어가 동작할 수 있도록 제어신호를 생성한다.

3. 저장장치(Register)

데이터를 임시 저장하는 공간으로 PC, IR, AC등 여러 레지스터가 존재한다.

클럭 사이클

한번의 연산은 하나의 클럭 사이클이 필요합니다. 이때 클럭(Clock)이란 각 연산의 동기화를 인한 신호로 연산의 타이밍(timing)을 제공합니다. CPU는 수많은 연산을 진행하는데 아래의 4단계를 반복합니다. 이들의 각 단계는 클럭에 맞춰서 진행됩니다. 물론 이후의 CPU는 이 4단계보다 훨씬 복잡한 단계로 연산이 진행되지만 기본 틀은 여기서 시작됩니다.

1. Fetch

CPU내부의 PC(program counter)가 가리키고 있는 명령어 주소를 메인 메모리(RAM)에서 찾아 CPU의 IR(instruction register)로 가져오고, PC가 가리키는 숫자가 올라간다.

(보통은 1씩 증가하지만 Loop나 함수호출과 같은 jump명령어로 순서가 바뀔 수 있다.)

2. Decode

IR에 저장된 명령어를 CU(control unit)이 디코딩을 하여 적절한 레지스터로 이동시킨다.

3. Execute

디코딩된 명령어를 ALU(Arithmatic Logic Unit)에서 연산을 한다.

4. Restore

연산이 완료되어 나온 결과를 레지스터나 메모리에 저장한다.

.

.

.

CPU 성능이 향상되기 위해서는 세가지 방법이 있습니다.

- 클럭 속도를 증가시킴

- 속도를 너무 많이 올리면 회로에서 오류가 발생할 가능성이 커지기 때문에 한정적이다.

- 내부 구조를 최적화시킴

- 슈퍼스칼라 방식과 파이프라이닝 방식이 내부 구조를 최적화한 방식이다.

- 멀티코어 CPU 개발

- 컴퓨터가 여러 개의 CPU를 가지고 있고, 각각의 CPU가 프로그램을 실행한다.

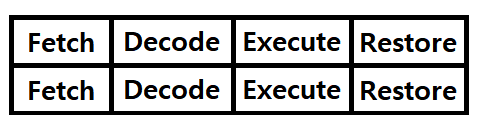

슈퍼스칼라

하나의 CPU에 ALU와 IR이 2개이상 존재한다. 즉 파이프라인(하나의 명령어 처리과정)이 여러개이기 때문에 명령어를 병렬 수행할 수 있다.

하지만 이 방식은 다른 데이터나 자원 등에 대한 의존성이 있는 경우 다른 파이프라인에서는 작업을 수행하지 못하기 때문에 의미가 없어진다.

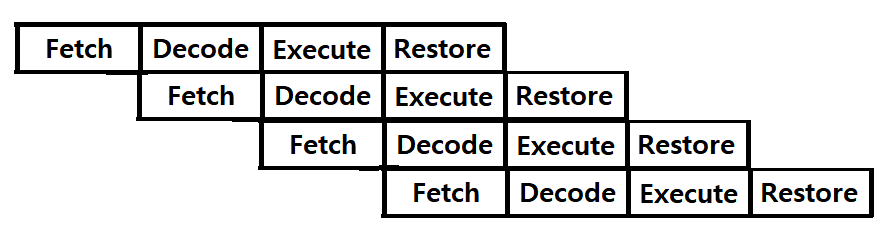

파이프라이닝

기존의 CPU 실행 사이클(클럭 사이클)에서 각 단계가 진행될 때 다른 단계에선 유휴 상태(idle)이기 때문에 자원의 낭비가 발생한다. 예를 들어 Fetch단계가 실행되는 동안 ALU는 아무것도 하지 않고 대기만 하고있다. 파이프라이닝은 이런 낭비를 막기 위해 각 유닛을 병렬적으로 동작시킨다. 이 방식은 거의 모든 CPU에서 채택하고 있다.

하지만 이 방식에도 단점이 있는데, 다음 명령어를 미리 실행하던 중 이전 명령어에서 jump명령어가 발생한다면 DECODE를 한 다음 명령어를 버려야하는 문제가 발생한다. 이는 자주 발생한다면 성능이 떨어지기 때문에 Loop를 피하는 것이 최선이다.

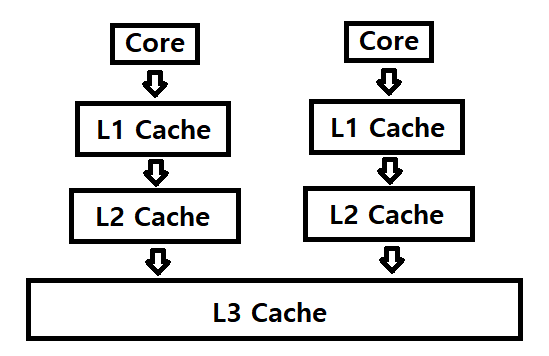

Cache 메모리

CPU와 메모리 사이의 속도차이를 완화하여 컴퓨터 성능을 향상시키기 위해 여러 Level로 cache 메모리를 두었다.

core(CPU)에서 원하는 데이터를 L1 cache에서 먼저 찾고, 없다면 L2, L3 순으로 넘어가며, cache 메모리에 없다면 그때 RAM에서 검색한다.

시스템 버스

CPU와 RAM은 버스를 통해 데이터를 주고받는다.

CPU가 데이터를 읽을 때는 Address Bus에 주소를 싣고 RAM에 전달하면, RAM은 해당 주소에 있는 데이터를 External Data Bus를 통해 CPU에 전달합니다.

CPU가 데이터를 RAM에 작성할 때는 Address Bus에 저장할 RAM주소를 넣고, 동시에 External Data Bus에 데이터를 실어 RAM에게 해당 주소에 데이터를 저장하도록 합니다.

참고문헌

https://en.wikipedia.org/wiki/Instruction_cycle

https://wikidocs.net/63816

https://m.blog.naver.com/PostView.naver?isHttpsRedirect=true&blogId=c_18&logNo=10185806568

https://ko.wikipedia.org/wiki/%EC%8A%88%ED%8D%BC%EC%8A%A4%EC%B9%BC%EB%9D%BC