배우게 될 것

High level langauage → assembly language (by assembler)

assembly language → binary machine language (by compiler)

binary language↔ high level language (가능) (by incoder/decoder)

Instructions Set

- 하드웨어에 명령을 내릴 때 instruction을 이용

- 컴퓨터 언어의 단어→instruction

- instruction의 집합 → instruction set. 다른 컴퓨터는 다른 instruction set을 가짐.

Instruction Set Architecture (ISA)

: 명령어 집합 구조.

하드웨어와 system software간의 추상적인 인터페이스로 instruction, register, I/O등을 포함한 기계어 프로그램을 작성하기 위해 필요한 모든 정보

다양한 기계에서, 서로 다른 CPU에서 동일한 소프트웨어를 구동 가능하도록 함.

MIPS(Microprocessor without Interlocked Pipeline Stages)

: MIPS technologies에서 개발한 명령어 집합체계(ISA : Instruction set architecture)

얘도 ISA의 일종. 다른 ISA 종류에는 ARM도 있음. 임베디드 시스템에 많이 쓰이고 있음.

MIPS를 이용하여 high level 언어에서 assembly 언어로, 그리고 기계어 언어로 전환

MIPS의 설계 원칙

1 ) 간단함을 위해 규칙적으로 만들자 → MIPS 코드를 예외없이 규칙적으로 해서 구현을 간결하게.

2) 작은 것이 빠르다 → register 32개인 이유는 최대한 clock cycle 줄이려고. 메인메모리에 비해 작지만 1000배 속도가 빠르다.

3) 반복적인 case를 빠르게 → 0이 자주 사용되니까 0 register를 만든다(값을 변경할 수 없는 constant 상수, 읽기만 가능.) MIPS 레지스터의 0번 레지스터는 항상 0이다. load instruction의 수를 줄여준다.

- 좋은 설계는 적당한 타협을 요구한다→ reg 32비트로 고정하면 남는 값이 생기더라도 고정된 것을 유지한다. (32비트는 4byte임.) →Immediate arithmetic과 load/store instruction은 별개의 작업이지만 I-format으로 모두 표현할 수 있다.다른 종류의 작업들을 한 포맷으로 표현하면 decode하는 것을 어렵게 만들지만 32-bit instruction들을 균일하게 해준다.

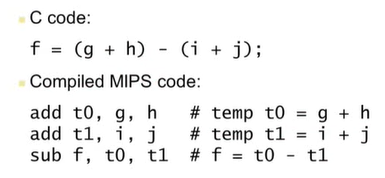

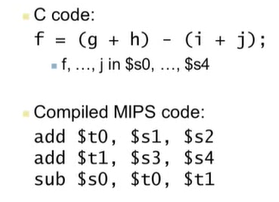

Arithmetic Operation (산술연산) in MIPS

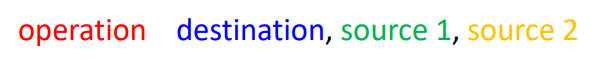

- 3개의 Operand : 2개의 source/ 하나의 destination & 하나의 Operation

- add a, b, c # a=b+c

- Arithmetic Operations

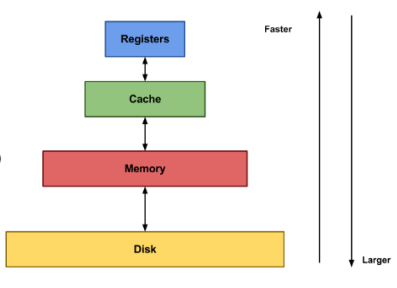

Register

- CPU가 요청을 처리하는데 필요한 데이터를 일시적으로 저장하는 장치

- 데이터를 빠르게 accept, transfer, store하기 위한 컴퓨터 메모리. CPU에서 빠르게 시행되어야 하는 instruction을 저장.

- 32비트로 레지스터의 개수는 고정(0번부터 31번까지). $ 뒤에 있는게 레지스터 이름

- 왜 레지스터 개수는 32비트인가? 레지스터 수의 증가는 clock cycle 시간을 증가시킨다. 따라서 실행 속도를 위해 필요한만큼만.

- temporary values : $t0, $t1, ... $t9. t0부터 순서대로 저장

- saved variables : $s0, $s1, ... $t7

- constant 값 0저장: $zero

Register Operands

→ 산술연산은 MIPS 명령어의 레지스터에서만 발생

→ data는 메모리에 있으므로 메모리와 레지스터 간에 데이터를 전송해주는 명령어가 MIPS에 포함되어 있어야 함.

→ 메모리의 Word(memory안에 저장되어 있는 값)에 액세스하려면 명령어는 메모리 주소를 먼저 제공해야 함.

→ 워드는 한번의 작업으로 저장장치에서 프로세서 레지스터로 데이터를 이동시키기 위한 단위이다

Memoryincluding the sign of the exponent Operands

Byte addresses

대부분의 아키텍처들은 메모리를 byte(8 bit)단위로 지정한다. 32bit 프로세서에서 메모리 주소들은 word(32 bit) 단위로 묶여진다.

워드는 CPU가 한번에 처리할 수 있는 데이터의 크기

를 의미하므로 워드의 크기는 CPU의 성능에 따라 달라진다.

메모리는 byte 단위로 접근(주소 한 칸은 byte로 이루어짐) 워드에는 4바이트가 있다.

MIPS는 각 바이트 (32비트, 4바이트)의 주소를 지정 하므로 워드 주소는 4의 배수

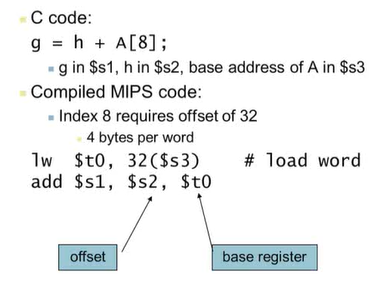

example1)

(1) array의 시작주소인 s3가 저장되어 있는 것이지 A[8]의 값이 저장된 것이 아니므로 임시저장소인 t0으로 워드를 불러온다.

(2) h와 A[8]을 더하고 g의 registor인 s1에 값을 넣는다.

lw : load word

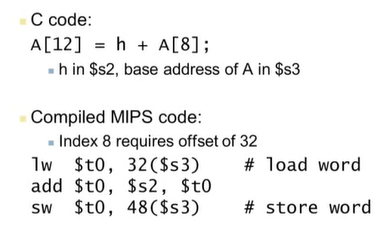

example2)

add한 값을 다시 temporary register에 넣고 store word를 한다.

sw : store word

Register vs. Memory

*메모리에 직접 접근하는 것보다 레지스터에 접근하는 것이 훨씬 빠름

*메모리의 데이터를 (레지스터에서) 이용하기 위해 레지스터에 데이터를 불러오고(load) 다시 메모리에 저장하는(store) 방법을 이용한다.

※ MIPS는 Load-Store Architecture이다.

ㆍLoad와 Store를 반복하므로, 많은 instruction들이 수행된다.

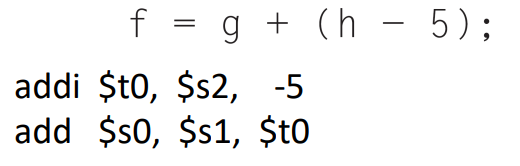

Constant or Immediate operand

- 프로그램에서 연산은 상수를 자주 사용

→ 산술 명령어에 상수 값을 포함하여 상수가 메모리에서 로드되는 작업을 생략한다.

- 단, 명령어는 add가 아닌 addi를 사용함.

- 뺄셈은 지원하지 않으므로 덧셈에 음수 값을 사용

→ Make common case fast의 예시

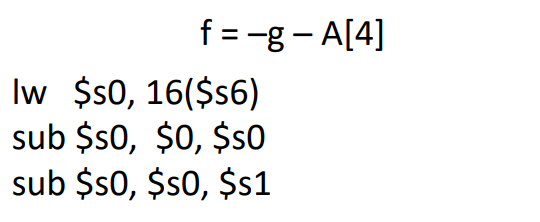

여기 s0 t0으로 바꿔야됨.

0에서 빼서 -를 만들어준다

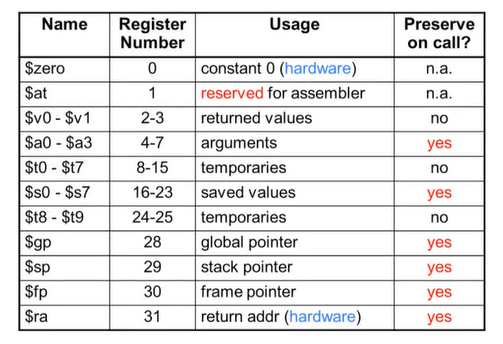

MIPS Register Convention

| 번호 | 이름 | 용도 | 호출 중에 값이 변하지 않는지 |

|---|---|---|---|

| 0 | $zero | 항상 0 (hardware) | n.a. (해당없음) |

| 1 | $at | 어셈블러만 사용하도록 예약된. (프로그래머는 X) | n.a. |

| 2~3 | v1 | 반환값 (서브루틴. 함수호출) | no |

| 4~7 | a3 | argument(매개값) (서브루틴. 함수호출) | yes |

| 8~15 | t7 | 임시 값들 (rvalue) | no |

| 16~23 | s7 | 저장되는 용도의 값 (변수, lvalue) | yes |

| 24~25 | t9 | 임시 값들 (rvalue) | no |

| 26~27 | k1 | OS 커널만 사용하도록 예약된. | no |

| 28 | $gp | global 포인터 | yes |

| 29 | $sp | stack 포인터 | yes |

| 30 | $fp | frame 포인터 | yes |

| 31 | $ra | 반환 주소 (hardware) | yes |

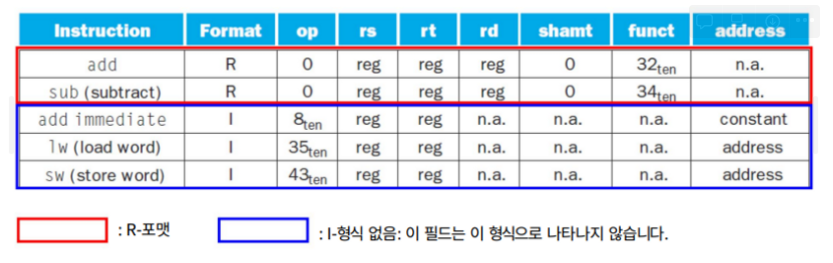

MIPS instruction

add 더하기

sub 빼기

addi 상수를 더하기

lw 메모리 워드를 레지스터로

sw 레지스터의 워드를 메모리로

Signed & Unsigned Numbers

- 인간은 10진법, 컴퓨터는 2진법

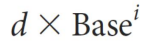

- 모든 진법에서 i번째 숫자 d

- LSB (Least significant bit) → MIPS 워드에서 가장 오른쪽 비트

- MSB(Most Significant Bit): MIPS 워드에서 가장 왼쪽 비트

Unsigned binary numbers(32비트)

- 2의 32승 개의 숫자표현 가능

- 범위: 0~2^n-1

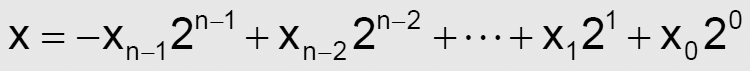

Signed binary numbers (32bit) - Negating(부호 반전)

- 부호가 있는 정수 표현 → 2의 보수 사용

- 범위: -2^(n-1)~2(n-1)-1

- MSB 1이면 무조건 음수. MSB가 1이고 나머지 0이었을때 가장 작은 음수, MSB 0이고 나머지 다 1일때 가장 큰 양수. 32비트가 1로 다 차도 -1 음수임.

- negating - 부호 반전 시킬 때 보수를 취하고 1을 더한다.

Signed binary numbers(32비트) - Sign extension

같은 수를 더 많은 비트를 이용하여 표현할 때

부호 비트와 같은 값을 왼쪽에 채워준다.

- MIPS에서의 Instruction set

- addi: immediate value를 늘림

- Ib, Ih: load byte/halfwork 늘림

- beq, bne: displacement를 늘림

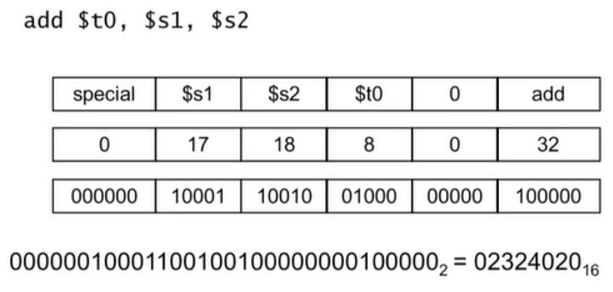

**Representing Instruction**

assembly 언어를 binary 언어로 incoding

-이 binary 언어를 기계어라고 부른다.

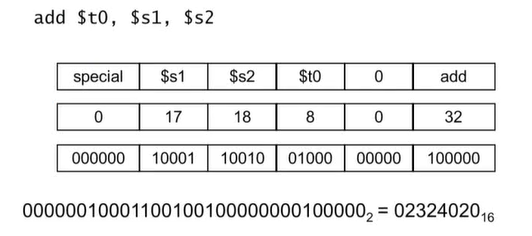

MIPS R-format Instructions

- 산술/ 논리 연산에 이용

- op: =operation code. 명렁어가 수행할 연산의 종류.

- rs: 피연산자1이 들어있는 레지스터 번호 (5 bit-32개의 레지스터)

- rt: 피연산자2가 들어있는 레지스터 번호 (’’)

- rd: 연산결과가 담길 레지스터 번호(’’)

- shamt: shift amount (필요없을 때는 0으로 채워짐)

- funct: =fuction code. opcode와 함께 어떤 종류의 연산을 할지

- ex)

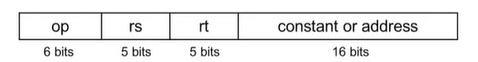

MIPS I-format Instructions

- immediate 연산과 데이터 전송(load/store)에 이용

- rt: destination 혹은 피연산자2 레지스터 번호

- constant: -2^15 ~ 2^15 - 1 의 수를 표현 가능

- address: rs에 담긴 base address로부터 얼마나 멀리있는지(offset)

→ 설계원칙 4 : 좋은 설계는 좋은 타협을 필요로

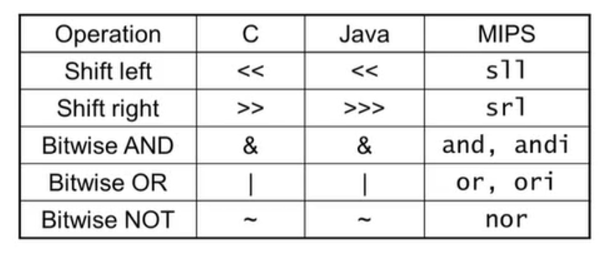

Logical Operation

bit 단위 조작을 위한 instruction.

→word에서 비트를 추출하거나 새로 집어넣을 때.

LSB를 왼쪽으로 옮길 때.. 등.

Logical Operation - Shift Operation

- 왼쪽으로 shift - sll

곱하기와 관련. 전체 비트가 왼쪽으로 이동하고 오른쪽의 빈 공간은 0으로

i 비트만큼 왼쪽으로 shift→ 2^i와 같음

- 오른쪽으로 shift-srl

나누기와 관련. 전체 비트가 오른쪽으로 이동하고 왼쪽 빈공간은 양수면 0, 음수면 1을 채워준다.

i 비트만큼 왼쪽으로 shift하면 2^i만큼 나눈 것과 같음

Logical Operation - AND

word에서 특정 부분의 비트를 뽑을 때.

둘다 1일때만 1 둘 중 하나라도 0이면 0

Logical Operation - OR

word에서 특정 부분을 포함시킬때.

둘 중 하나라도 1이면 1.

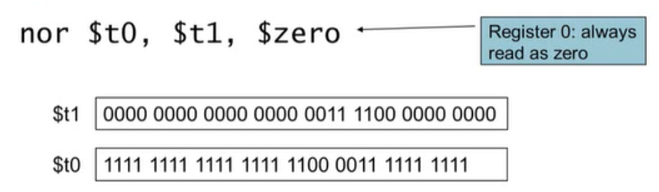

Logical Operation - NOR

word 비트 모두 반전시킬 때

둘다 0일 때 1, 둘 중 하나라도 1이면 0.

MIPS는 NOT operation이 없어서 NOR 3항 연산으로 구현된다.

0과 nor하면 보수화가 됨.

Instructions for Making Decisions

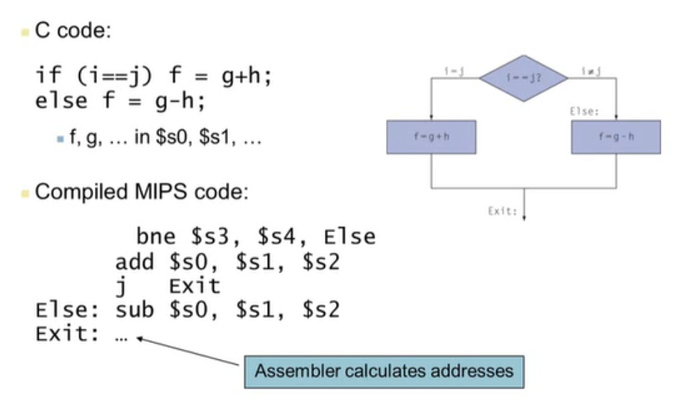

Conditional Operation(if문)

- beq(branch if equal) : 만약 register1의 값(rs) == register2의 값(rt)라면, L1이라고 표시된 instruction으로 이동

- bne(branch if not equal): 만약 register1의 값(rs) != register2의 값(rt)라면, L1이라고 표시된 instruction으로 이동

- j L1 : 무조건 L1으로 표시된 instruction으로 이동.

- ex) if statement by MIPS code

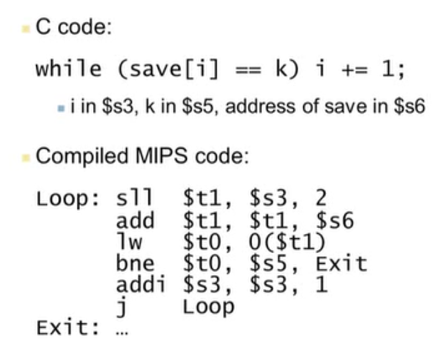

Compiling Loop Statements(while문)

i*4를 해서 메모리에 접근할 수 있도록 한다.

base address에 4i를 더해서 save[i]의 주소에 접근한다 t1=save[i]

save[i] 값을 t0에 load word한다. (t1은 save[i]의 주소이지 값이 아니다._

bne를 통해서 save[i]랑 k랑 같지 않으면 EXIT

addi 같으면 i에 1을 더한다.

j Loop loop로 다시 돌아간다. bne가 만족되지 않으면 계속 반복해서 수행한다.

Comparison instruction

slt t0, $s3, $s4 ⇒ if $s3<s4면 t0=1. 만족 안하면 0을 대입.

- signed: slt, slti 1번째 레지스터와 2번째 레지스터의 값 비교

- unsigned: sltu, sltui: 1번째 레지스터와 2번째 레지스터의 값 비교

- i 붙은거는 immediate 연산에서 constant 값과의 비교

교수님이 따로 추가코드 써주신 것도 다시 보기.

이 글은 경희대학교 김정욱 교수님의 컴퓨터구조 수업을 바탕으로 작성되었습니다.