1. IPU hardware overview

IPU는 머신 러닝 애플리케이션 가속화를 목적으로 설계된 대규모 병렬 처리 및 메모리 중심 구조를 기반으로 한다. 혼합 정밀도 데이터 (mixed-precision data)에 대한 매우 높은 성능의 부동 소수점 연산 능력을 제공한다. 또한 IPU에는 데이터에 대한 빠르고 유동적인 접근을 가능케 하는 엄청난 양의 분산형 SRAM이 장착되어 있다.

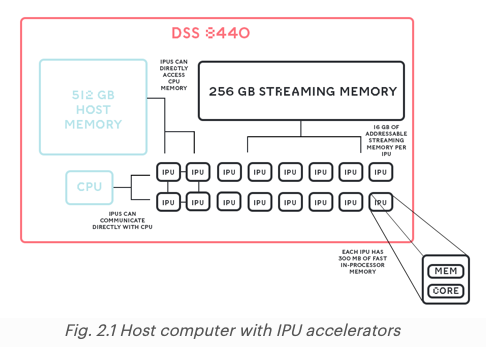

IPU는 호스트 컴퓨터용 가속기로 사용된다. 호스트 프로세서는 하나 이상의 IPU에서 실행되는 IPU 코드를 생성할 수 있다. 이를 통해 호스트는 IPU에서 연산을 수행하고, IPU는 호스트 메모리와 데이터를 주고받을 수 있다.

단일 IPU는 광범위한 기계 학습 및 인공 지능 관련 task를 수행할 수 있다. 또한, 다중 IPU는 한꺼번에 단일 task를 처리할 수 있다. 이 경우에 다중 IPU는 custom IPU-Link® interconnect cable을 통해 서로 통신한다.

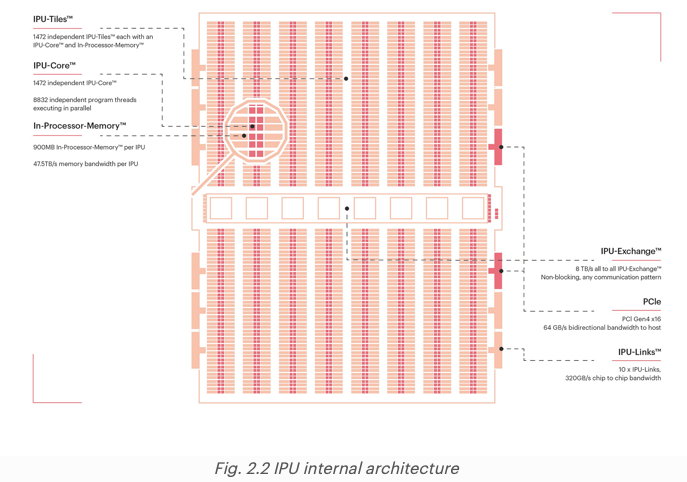

IPU는 tile이라고 불리는 여러 개의 독립 처리 장치로 구성되어 있다. 모든 tile들은 exchange라고 불리는 초고속의 다대다 communication fabric으로 연결되어 있다. 다중 IPU가 서로 통신할 때, exchange fabric은 모든 IPU에 존재하는 모든 tile로 확장한다.

1.1. Tile architecture

각각의 tile은 지역 메모리와 단일 프로세서로 구성되어 있고, 임의적인 실행 흐름을 갖는 독립 프로그램을 실행할 수 있게끔 하는 완전한 프로세서이다.

이 프로세서는 라운드 로빈 방식으로 서비스되는 하드웨어 쓰레드를 지원한다. 메모리 접근 방식과 대부분의 명령어는 단일 사이클로 이뤄진다. 코드는 supervisor 모드와 worker 모드로 실행될 수 있다. supervisor 코드는 부동 소수점 연산을 수행하는 worker task의 실행을 제어한다.

해당 프로세서의 명령어 집합은 처음부터 기계 학습과 인공지능을 지원할 목적으로 설계되었다. 이 프로세서는 단정밀도 (32bit)와 반정밀도 (16bit) 부동 소수점 연산을 수행한다. 이 연산은 벡터화되고, 사이클당 최대 32개의 단일 곱셈 누산기까지 사용할 수 있다. 초월수 및 랜덤 숫자 생성과 stochastic rounding (확률적 반올림)에 대한 하드웨어 지원 또한 존재한다.

1.2. Memory architecture

각각의 tile은 로컬 SRAM을 갖고 있다. 이 지역 메모리는 tile 명령어에 직접 접근할 수 있는 유일한 메모리이다. 이는 tile에 사용되는 코드와 데이터에 모두 활용된다.

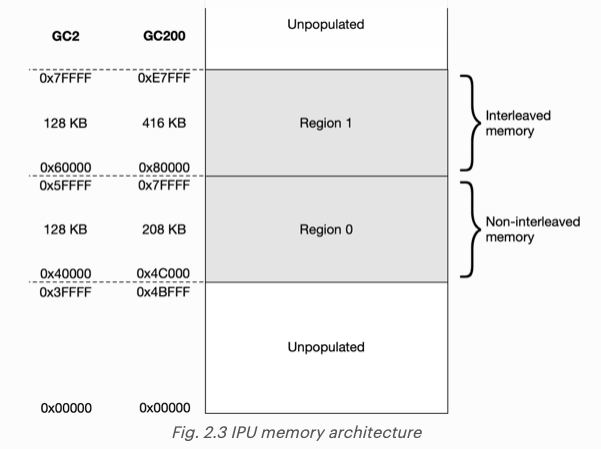

tile은 0x0부터 시작되는 연속적인 unsigned 21-bit 주소 공간을 사용한다. 실제로, 이 메모리 공간의 일부분만 메모리로 채워져 있다. 채워지지 않은 메모리 주소에 접근하는 것에 대한 효과는 아직 확인되지 않았다.

해당 메모리는 64-bit wide bank로 구성된 두 구역으로 구성되어 있다. Region 1의 bank에는 3비트 주소인터리빙 방식이 적용되어 있으며, 인터리빙은 홀수 word만큼 떨어져 있는 한 두 64-bit 주소에 동시에 접근할 수 있도록 만들어준다. 이는 예를 들면, 두 개의 서로 다른 뱅크에서 연속된 word를 읽기 때문에 128-bit load를 수행할 수 있다는 것을 의미한다.

모든 load, store 작업은 정렬되어야 한다. 명령어들은 Region 0에서만 fetch될 수 있다.

1.2.1. GC2 (Mk1) IPU memory

GC2에서, 각각의 tile은 256KB의 SRAM을 가지고 있다. 이는 1,216개의 tile을 가진 IPU는 총 약 300MB의 메모리를 갖는다는 것을 의미한다.

사용 가능한 메모리의 주소는 0x40000에서 시작하고 0x7FFFF에서 끝난다. (Non-zero start address는 유효하지 않은 null pointer에 접근하는 것을 방지하는 간단한 방법이다.)

1.2.2. GC200 (Mk2) IPU memory

GC200에서, 각각의 tile은 624KB의 SRAM을 가지고 있다. 이는 1,472개의 tile을 가진 IPU는 총 약 900MB의 메모리를 갖는다는 것을 의미한다.

사용 가능한 메모리의 주소는 0x4C000에서 시작하고 0xE7FFF에서 끝난다.

1.2.3. Parity errors

메모리 패리티 에러는 데이터를 메모리에서 읽을 때, 예를 들면, load instruction 또는 instruction fetch 단계에서 발생한다. fetch된 명령어에서 탐지된 패리티 에러는 해당 명령어가 실행되지 못하게 한다.

패리티는 해당 디바이스의 전원이 켜지거나 리셋될 때 초기화된다.