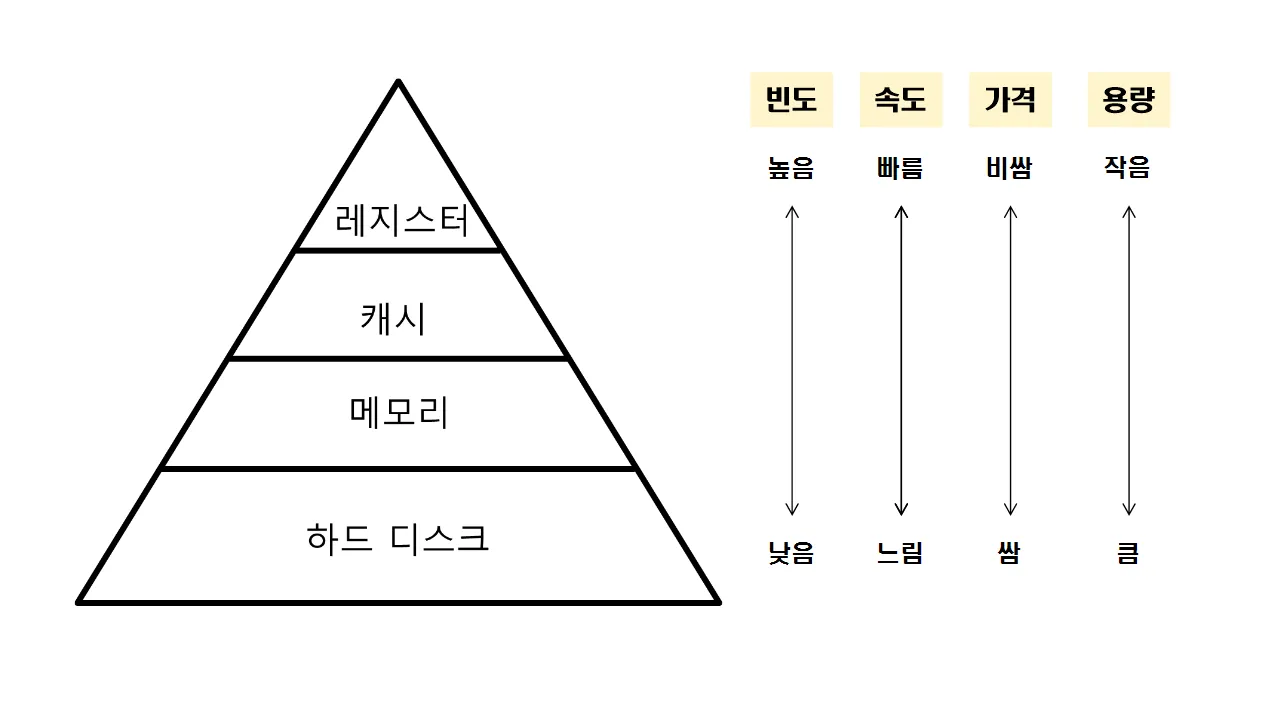

메모리 계층 구조(Memory Hierarchy)란?

| 명칭 | 위치 | 접근 속도 |

|---|---|---|

| 레지스터 | CPU 내부 | 빠름 |

| 캐시 | CPU 내부 | 빠름 |

| 메모리 | CPU 외부 | 레지스터와 캐시보다 느림 |

| 하드디스크 | CPU 직접 접근 불가 | 데이터를 메모리로 이동시켜 접근 가능 |

레지스터(Register)

개념

- CPU가 요청을 처리하는 데 필요한 데이터를

일시적으로 저장하는 기억장치CPU(Central Processing Unit): 중앙처리장치

CPU는 컴퓨터에서 4대 주요 기능을 관할하는 장치기억해석연산제어

CPU는 자체적으로 데이터를 저장할 능력이 없으므로 메모리로 직접 데이터를 전송할 수 없음

-> 연산을 위해 반드시레지스터를 거쳐야하며,

이를 위해레지스터는 특정 주소를 가리키거나 값을 읽어올 수 있음- 프로세스에 위치한

고속 메모리로, 프로세스가바로 사용할 수 있는 데이터(소량의 데이터, 처리중인 중간 결과등)을 담고있는 영역

- 프로세스에 위치한

CPU 내부 레지스터 종류

| 종류 | 설명 |

|---|---|

| 프로그램 계수기(PC, Program Counter) | 다음에 실행할 명령어(instruction)의 주소를 가지고 있는 레지스터 |

| 누산기(AC, ACcumulator) | 연산 결과 데이터를 일시적으로 저장하는 레지스터 |

| 명령어 레지스터(IR, Instruction Register) | 현재 수행중인 명령어를 가지고 있는 레지스터 |

| 상태 레지스터(SR, Status Register) | 현재 CPU의 상태를 가지고 있는 레지스터 |

| 메모리 주소 레지스터(MAR, Memory Address Register) | 메모리로부터 읽어오거나 메모리에 쓰기 위한 주소를 가지고 있는 레지스터 |

| 메모리 버퍼 레지스터(MBR, Memory Buffer Register) | 메모리로부터 읽어온 데이터 또는 메모리에 써야할 데이터를 가지고 있는 레지스터 |

| 입출력 주소 레지스터(I/O AR, I/O Address Register) | 입출력 장치에 따른 입출력 모듈의 주소를 가지고 있는 레지스터 |

| 입출력 버퍼 레지스터(I/O BR, I/O Buffer Register) | 입출력 모듈과 프로세서 간의 데이터 교환을 위해 사용되는 레지스터 |

캐시(Cache)

개념

- 데이터나 값을

미리 복사해놓는 임시 장소 - 시스템의 효율성을 위해 사용한다.

캐시 접근 시간에 비해원래 데이터를 접근하는 시간이 오래 걸리는 경우- 값을 다시 계산하는

시간을 절약하고 싶은 경우

속도가 빠른 장치와느린 장치사이에서속도 차이의 따른 병목현상을 완화하기 위한 범용 메모리

캐싱이란?

캐시 메모리 영역으로 데이터를 가져와 접근하는 방식이다.

캐시 종류

-

CPU 캐시- 대용량의 메인 메모리

접근을 빠르게하기 위해 CPU 칩 내부나 바로 옆에 탑재하는 작은 메모리 - 하드웨어를 통해 관리한다.

종류 설명 CPU에 직접적인 영향 L1 캐시 일반적으로 CPU 칩 안에 내장되어 데이터 사용 및 참조에 가장 먼저 사용되는 캐시 메모리 O L2 캐시 L1 캐시 메모리와 용도와 역할이 비슷하다. 속도 : L1 캐시> L2 캐시 > 일반 메모리(RAM) O L3 캐시 L1캐시, L2 캐시와 동일한 원리로 작동한다. CPU내장이 아닌 메인보드에 내장 되어있다. X - 대용량의 메인 메모리

-

디스크 캐시(디스크 버퍼)

하드디스크에 내장된작은 컴퓨터(디스크 제어, 외부와의 인터페이스 관리)가 소유한작은 메모리(디스크에 입출력되는 데이터를 저장하는 작은 메모리)

캐시 히트(hit)와 캐시 미스(miss)

캐시 히트

캐시에서 원하는 데이터를 찾았을 때 제어장치를 거쳐 가져오게 하고,

CPU 내부 버스 기반으로 작동하기 때문에 빠르다.캐시 미스

찾는 데이터가 캐시에 없을 때 주 메모리에서 다시 찾아오는 것을 말한다.

시스템 버스 기반이기 때문에 느리다.

캐시 매핑

캐시가 히트되기 전에 매핑하는 방법을 말한다.

- RAM은 레지스터에 비해 크기 때문에 Register가 캐시 계층으로 역할을 잘 수행하기 위해 매핑법이 중요하다.

| 이름 | 설명 |

|---|---|

| 직접 매핑 (directed mapping) | 메모리 1~100영역이고 캐시 1~10 영역이면 1 : 1~10 , 2 : 11~20 방식의 매핑을 말한다. 메인 메모리를 일정한 크기의 블록으로 나누고, 각각의 블록을 캐시의 정해진 위치에 매핑하는 방식이다. 구현이 쉽고 접근 속도가 빠르지만 교체를 자주하기 때문에 충돌이 잦고 적중률이 낮다. 캐시 메모리가 대용량인 경우에만 직접 매핑을 사용한다. |

| 연관 매핑 (Associative Mapping) | 순서를 일치시키지 않고 관련있는 캐시와 메모리를 매핑하여 메모리 내용이 캐시의 어느 위치에도 올라갈 수 있다. 충돌은 적고 적중률이 높다. 하지만 찾는 과정이 직접 매핑에 비해 오래걸린다. 전체 블록 탐색을 거쳐야하기때문에 느리다. |

| 집합 연관 매핑 (set associative mapping) | 직접 매핑 + 연관 매핑의 방식이다. 순서 일치 + 집합을 둬서 블록화 후 저장한다. |

메인 메모리(Main Memory)

개념

주기억장치(1차 기억 장치)- 컴퓨터에서 수치, 명령, 자료등을

기억하는 컴퓨터 하드웨어 장치

구성

- RAM(Random Access Memory) : 휘발성 기억 장치

- 컴퓨터가

빠른 접근을 하기 위해 데이터를단기간 저장하는 구성요소 - 사용자가 요청하는 프로그램이나 문서를

스토리지 디스크에서메모리로 로드해 각 정보에 접근한다. 전원이 유지되는 동안 CPU의 연산 및 동작에 필요한모든 내용을 저장한다.전원 종료시 기억된 내용삭제Random Access: 어느 위치에서든 똑같이 접근해 읽고 쓸 수 있다는 의미다.

- 컴퓨터가

- ROM(Read Only Memory) : 고정 기억 장치

- 컴퓨터에 지시사항을

영구히 저장하는비휘발성 메모리 전원 종료시 기억된 내용유지변경 가능성이 희박한 기능 및 부품에 사용- 소프트웨어 :

초기 부팅관련 부분 - 하드웨어 : 프린터 작동에 관여하는

펌웨어 명령등

- 컴퓨터에 지시사항을

하드 디스크 드라이브(Hard Disk Drive, HDD)

개념

하드 디스크(Hard Disk),하드 드라이브(Hard Drive),고정 디스크(Fixed Drive)비휘발성,순차 접근이 가능한 컴퓨터의 보조 기억 장치- 비휘발성 데이터 저장소 가운데 가장 대중적이며 용량 대비 가격이 가장 저렴

작동 원리

- 보호 케이스 내부의 플레터를 회전 -> 플래터에

자기 패턴으로 정보 기록한다. - 플래터 표면의 코팅된 자성체에

데이터 기록한다. - 회전하는 플래터 위에 부상하는

입출력 헤드에 의해 자기적으로데이터 기록 및 조회 가능하다.

구성 요소

| 요소 | 설명 |

|---|---|

| 제어회로 | 하드디스크의 총괄적인 부분을 제어하는 회로이다. 제어회로 내부의 하드 디스크에 입출력될 데이터를 임시 저장한다. |

| 스핀들 모터(spindle motor) | 플래터의 회전을 담당하는 부분이다. |

| 플래터(Platter) | 데이터 기록을 담당한다. 하나의 하드디스크에 한 개 이상 장착한다. 플래터 수가 늘어나면 용량 저장 크기도 늘어나고, 안정성은 떨어진다. |

| 액츄에이터(Actuator) | 제어회로 명령에 따라 액추에이터 암을 구동시킨다. 헤드가 원하는 데이터 조회가 가능하다. |

| 액츄에이터 암(Actuator Arm) | 액츄에이터에 의해 구동된다. 하나의 디스크에 여러 개 달려있다. 암의 끝 부분에 입출력을 위한 헤드 달려있다. |

| 헤드(Head) | 데이터를 읽고 쓰는 헤드 |

메모리 계층 구조의 필요성

디코딩(명령어 해독 단계) 속도

디코딩(decoding):복호화라고도 하며,부호화(Encoding)된 정보를 부호화되기 전으로 되돌리려는 처리 혹은 처리 방식이다.

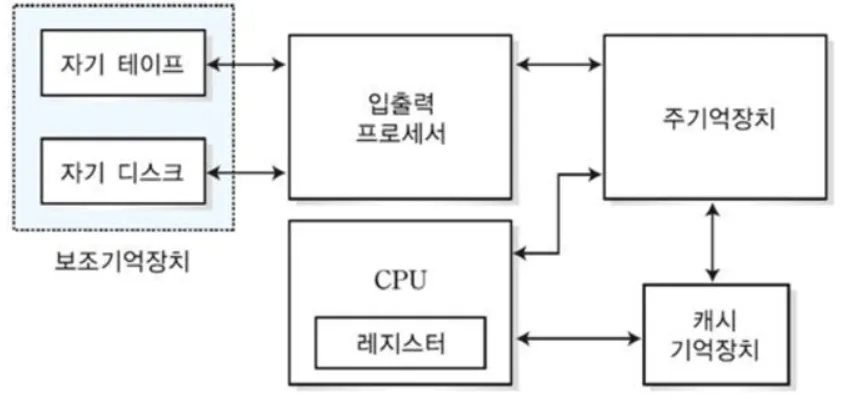

CPU의 메모리 접근 방식

-

CPU는 3개의 버스를 통해 메모리에 접근한다.

주소 전달 버스: CPU가 메모리의 어느 부분의 데이터를 접근하는지를 담당한다.데이터 전달 버스: 메모리와 CPU 간 데이터 전송을 담당한다.컨트롤 신호 버스: CPU의 메모리 접근 여부를 담당한다.

-

주소 전달 버스 및 데이터 전달 버스에 값이 존재하고 컨트롤 신호를 전송한다.

-> CPU와 메모리 업무를 수행한다. -

CPU가 메모리에 접근하기 위해서는

Control bit가 필요하다.

-> 메모리의 크기가 크다면Decoding을 통해Control bit를 전달해야한다.

-> Decoding 과정에서시간이 소요된다.

-> 메모리의 크기가클수록 더 복잡한Decoding 과정이 필요하다. -

큰 메모리 용량을 사용하는 경우 디코딩하는 데 더 많은 시간이 소요된다.

->CPU가빠르게 데이터에 접근하기 위해서는 데이터를 저장하는메모리가 작아야한다.

자주 쓰이는 데이터는 계속 자주 쓰인다.(참조의 지역성)

-

큰 메모리를 사용한다고 해도 그 안의 데이터를

고르게 접근하지 않는다. -

자주 쓰이는 데이터는

계속 자주 쓰이고, 자주 쓰이지 않는 데이터는계속 자주 쓰이지 않는다.

=> CPU는 자동으로 자주 쓰이거나 쓰일 것 같은 데이터를 메모리에서 캐시로 읽어온다.

이를 이용해자주 쓰일 것 같은 데이터를 모아작은 메모리 안에 구성한다면시간과 공간의 효율을 높일 수 있다. -

자주 쓰이는 데이터는

전체 데이터 양에 비해 작은 양이므로 캐시는 메모리보다, 메모리는 하드디스크보다 더 작아도 된다.

경제성

-

메모리 구조에서 상층에 속할수록

더 비싸다. -

메모리 계층 구조의 모양이 피라미드인 이유이다.

- 비싼 하드웨어는 꼭 필요한 크기만큼만 사용한다.

- 싼 하드웨어를 넉넉한 크기만큼 사용했다.