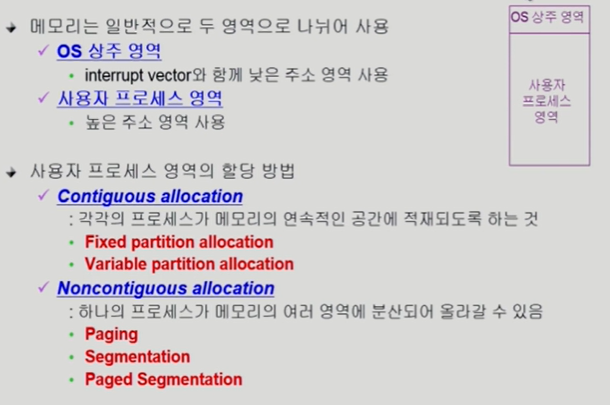

Allocation of Physical Memory

Contiguous Allocation

현대 운영체제들이 잘 사용하지 않는 방법이다. 프로그램을 구성하는 가상 메모리 주소 공간이 물리적인 메모리에 통째로 올라가는 방법이다. 이때는 메모리 주소 변환이 비교적 간단하다. 각각의 프로그램마다 0번째부터 시작하는 독자적인 메모리 주소공간이 있는데 시작위치만 알면 쉽게 변환할 수 있다.

불연속 할당은 프로그램이 조각 조각나서 부분 부분을 물리적인 메모리에 올리는 것이다. 프로세스를 구성하는 주소 공간이 동일 페이지로 쪼개져 있다.

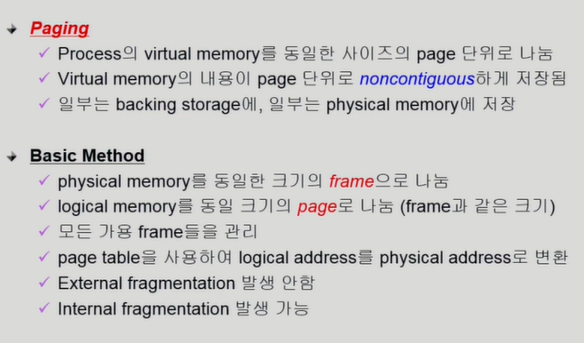

Paging

프로세스 각각의 메모리 공간을 페이지로 잘라서 물리적 메모리에 올라갈 수 있게 한것이다. 물리적인 메모리도 잘라놔야 한다 이를 frame이라 한다 (크기는 주로 4kb).

외부조각이 생기지 않는데, 외부 조각은 메모리에서 너무 작아서 프로그램이 할당 받을 수 없는 공간이고 내부 조각은 할당 받았지만 사용하지 않는 공간이다. 페이징 기법에서는 적어도 외부 조각은 생기지 않는다.

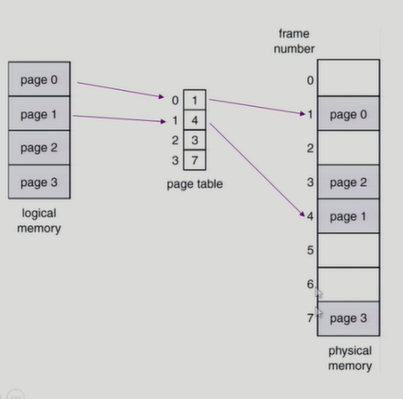

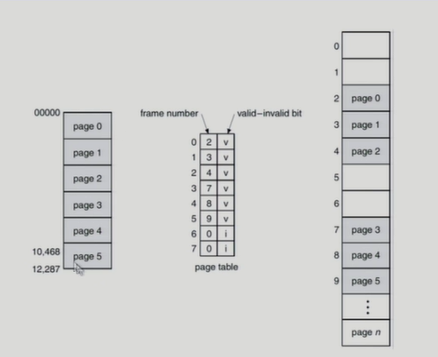

Paging Example

테이블은 그냥 배열이라고 생각하면 된다. 어떨 때는 물리적인 프레임에 안올라가 있을 수도 있는데 그러면 페이지 테이블에 있는 숫자가 의미 없는 숫자가 된다. 이를 유효한지 나타내는가는 valid bit으로 표현되는데 뒤에 나온다.

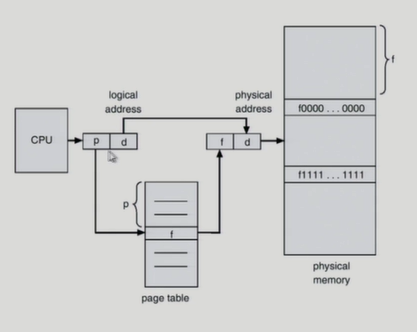

Address Translation Architecture

cpu가 보는 주소는 프로그램이 보는 논리적인 주소인데 페이지 테이블을 통해서 물리적인 메모리로 바꾼다. 이 과정에서 p는 page 번호, d는 페이지 내의 offset을 의미한다. 페이지 번호가 바뀌어도 페이지 내부에서 얼마나 떨어져있는지는 바뀌지 않기 때문에 d는 안바뀌는 것이다.

logical address는 비트 단위로 논리적인 메모리를 구분한다. 32비트면 2^32 칸을 나눌 수 있으므로 대략 4(2^32 * byte)기가정도이다.

4기가 바이트를 4kb로 나누면 대략 1메가, 즉 100만개가 나온다. 프로세스를 구성하는 페이지가 100만개가 나온다는 것이다. 그러면 페이지 테이블에 100만개의 엔트리가 필요하다는 것이다.

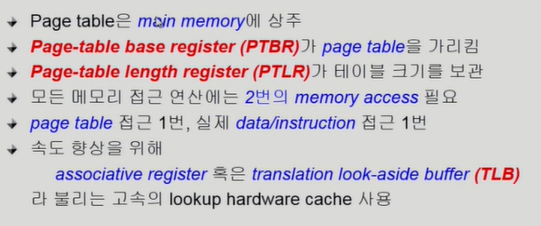

Implementation of Page Table

메모리에 한 번 접근하려면 테이블에 한번 접근, 실제 데이터에 접근으로 2번 접근해야한다. 이는 성능 저하로 이어진다.

성능 저하를 막기 위해 주소 변화를 위한 캐시를 두고 있다. 이를 TLB (Translation Look-aside Buffer)라 한다.

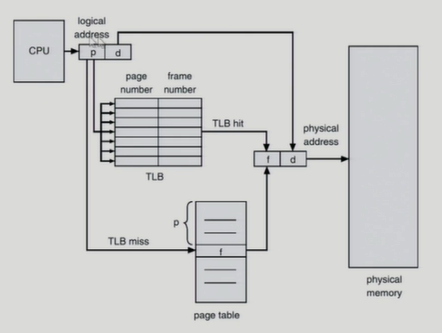

Paging Hardware with TLB

물론 TLB에 없으면 page table에서 가져와야 한다.

TLB는 page table과 달리 인덱스로 접근하는 것이 아니다. 그래서 페이지 번호와 프레임 넘버 둘 다 가지고 있어야 한다. 또한 p에 대한 자료가 있는지 전부 찾아봐야 한다. 하나하나 찾으면 너무 느리니 associative register라는 병렬적 탐색이 가능한 hardware로 탐색을 한다.

page 테이블은 프로세스마다 존재한다. context switch가 되면 tlb는 다 바뀌어야 한다. context switch의 주요 overhead 이유다.

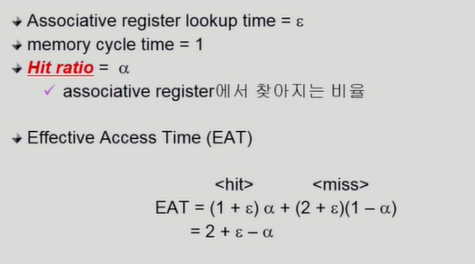

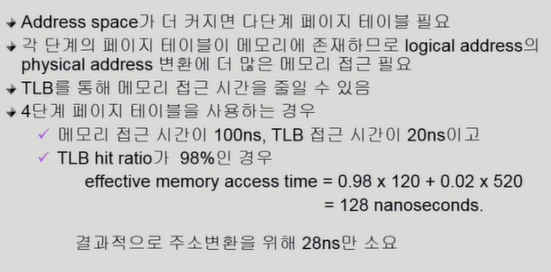

Effective Access time

보통 hit ratio는 1에 가깝다.

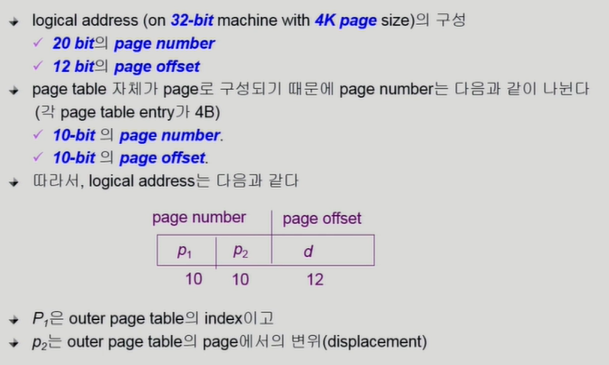

Two-Level Page Table

page table이 100만개 이상되는데, 각 프로세스마다 page table을 가지고 있으니 공간 낭비가 심하다 (프로세스마다 4mb이상).

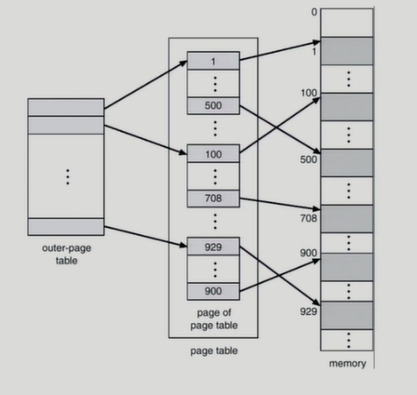

논리적인 주소를 주면 바깥쪽 table page와 안쪽 page table 두 번을 거치고 실제 데이터를 가져 온다. 시간상으로는 손해지만 공간상으로는 이득이다.

왜 공간상으로 이득일까? 페이지의 주소 공간 100만개 중 실제로 사용되는 것은 얼마되지 않는다. 사용되지 않는 페이지도 페이지 테이블에서 엔트리를 만들어야 하기 때문에 페이지 테이블의 공간 낭비가 생긴다. 2단계 페이지 테이블에서는 사용이 안되는 페이지에 데해서는 페이지 테이블이 만들어지지 않고 그냥 널로 되어있다.

안쪽 페이지 테이블 크기의 하나는 4kb이다. 그 내부의 크기는 4 byte이므로 1k가 나온다.

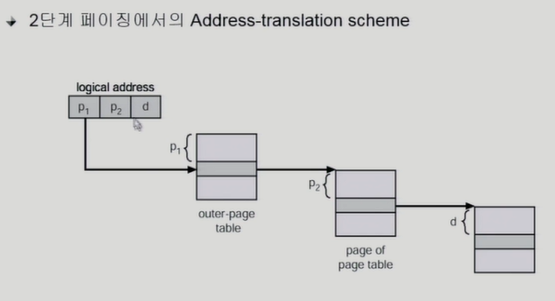

Address-Translation Scheme

맨 뒤의 d는 page offset이다. 페이지 내에서 얼마나 떨어져있는가. 4kb (2^12)를 구분해야기 때문에 d는 12비트다. page of page table 하나가 페이지화 되어서 들어가기 때문에 4kb이다. 각각의 엔트리가 4 byte기 때문에 2^10개의 엔트리가 존재한다. 따라서 p2가 10이 된다. p1은 나머지를 차지한다. outer page의 시작위치는 page-table base register가 가지고 있다.

Two-Level Paging Example

Multilevel Paging and Performance

다단계 페이지 테이블을 이용하면 공간을 줄일 수 있는데 시간이 오래 걸린다.

TLB에 진짜 쓰이는 것들만 정보를 갖고 있으면 hit ratio가 올라가서 시간을 줄일 수 있다.

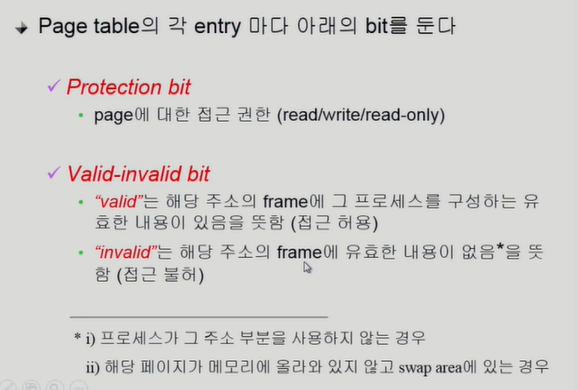

Valid (v) / Invalid (i) Bit in a Page Table

위에서 말했던 내용이다.

valid-invalid bit으로 실제 메모리에 올라가있는지 확인하는 것이다. 메모리에 올라가있지 않거나 또는 그 페이지를 안써도 invalid라고 되어있다.

Memory Protection