NVME Seminar #1

장치를 서버에 꼽고 test 를 하기위해 인식을 해야한다. Pcie , nvme 를 기반이 중요하다.

시스템 레벨에서의 device 초기화 과정이다. 전문가들에게도 내용 검증을 받을것이다.

전체적인 초기화를 보고

기본적으로 pcie 인데, application으로 쓸때는 nvme 로 써야하기때문에,

자료의 순서대로 host에서는 진행이 된다.

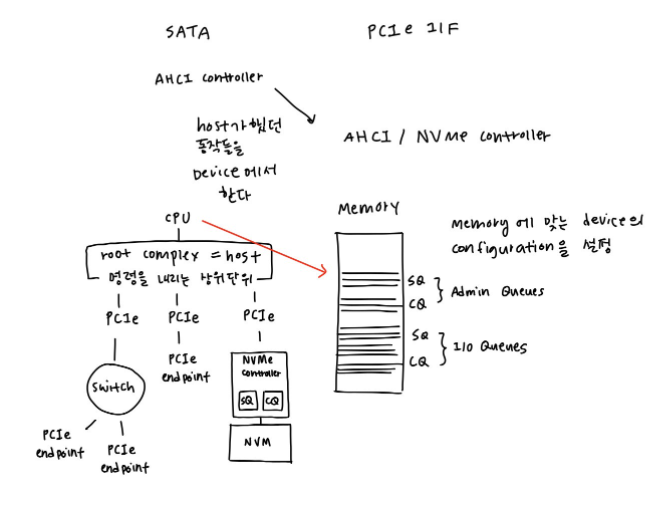

Overview를 보게되면, 처음에는 sata를썼지만, 현재는 pcie-nvme를 사용을한다.

예전에는 drive를 AHCI controller가 있었다 sata 는 호스트쪽에서 controller했던 부분이

밑으로 내려오게되었다. Nand, dram 이

Ssd를 완벽하게 사용하기 위해서는 속도, (pcie interface에서) application nvme 라는것,

Device 가 하는 전환이되서 ssd는 개발이 되어있다.

Pcie가 어떻게 동작하는지 알아야만 nvme 를 이해할수가 있다.

Serial -> parallel 로 pcie로

Root complex(host다) 여러가지가 있는데, 와이파이도 있고 등등… 다 pcie interface 로 통일된다.

Pcie는 endpoint, 거기서 ssd고, nvme 를 사용한다고 생각

storage에는 다른 interface 가 있다.

Server 가 어떻게 구성되었느냐에 따라 다를수있다.

Root complex 는 hw라고 일단 생각하면된다. Pcie는 destination 이라고 하고 root complex는 주체여서 이것은 결국에 큰 명령을 내리는 단위 – 이안에는 driver 도될수있고

Hw,sw – control center 이고

Switch 는 중간에 bridge같은 개념

메모리로 통신을 하게된다. 처음에 어떻게 사용을 할지를, 처음에 약속한다. 여기서부터 여기는 admin, IO, command를 읽어오는 형식 – 이 시점에서 memory 에다가 저런식으로 doorbell에는 queue 라는 개념이 nvme only이다. 기본 set을 주는게 pcie이다.

Graphic card다. -> direct로 통신을 하게되면,

어ㄸㅓ한 값이 설정이 되야지만, admin, io 가 된다. Q id 는 여기야 여기야 이런식으로 그 기반으로 알아서 read를해야했는거,

Mechanism 이

다른것들은 MMIO 가 아닐수도있다. – 프로토콜 방식이

처음으로 진행을 해야하는건

제품을 꼽고, 파워를 넣으면, host는 device가 있는지 파악

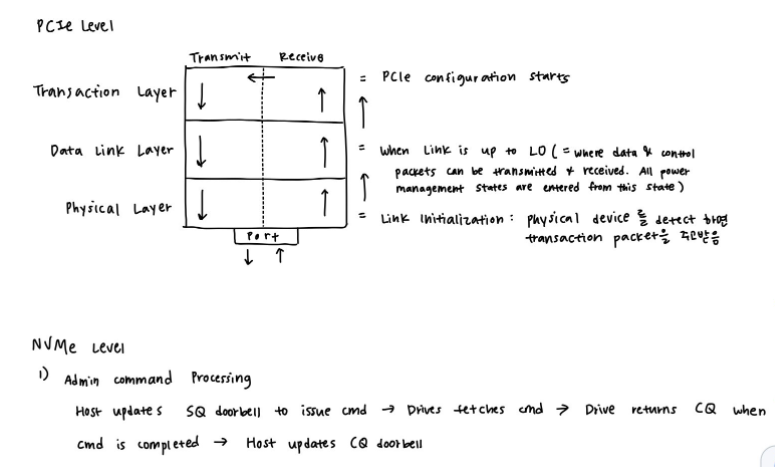

Link init 과정에서 phy하게 잡는다.

Lock을 잡는다. 0하고 1을 가지고 통신을 하는데, timing이라는게 있기 때문에, 서로 규약된 내용들이 있다.

Power 를 키면 phy layer 에서 rx/tx통신, electrical ㅎ

X4 x16, gen3, gen 4 등등

Data link 로 넘어가서 서로 유효성잇게 되는지 확인

그다음에 대한 0과 1에 대한것을 Transaction

Detect 하는건 쌍방에서 detect을 하게된다. tx에서 signal 확인 rx확인

양방에서 connection을 확인을 한다. (상호작용하는 형태)

Trace View – Host

조금 pcie가 특이한게,

서로 중간에 주고받는걸 중간에서 capture한 내용들이 Trace

PCIE단에서 logic anaylzre 라고 생각하면된다.

다른 기능들을 보면low level들을 볼수있다.

처음에 power on -> reset signal

서로 sync를 맞추기위해서 많은 신호들을 보낸다.

Consecutive를 주고받아야 그다음으로 넘어가고 넘어가고 ….

그래서 lane이 도대체 몇개야, device 가 4개를 지원해도 host가 2개 면 2개로 하는 communication을 진행

가장 낮은거에서 gen1, 에서 시작 그럼 8기가네 등등 둘다의 ㅁmaximum 으로 맞추는거다.

Gen1 -> gen2 -> gen3 까지 확인을 하게된다.

Lane이 몇개고 , interface speed 가 몇개 까지 될수있는것들…. 그걸 체킹하는 과정들이 쭉있다. Speed가 올라가면 올라갈수록 signal이 뭉개지니까 서로 작업들을 진행하는

Equalization 을 해서 최대한 valid 한 내용들을 만든내용들

많이 들어오면

Notation 에 대해서 보면 ㅇ32TS

R-> : 이건 root 에서 device로

R<-: device 에서 root로 갔다.

8.0GB는 – gen 3세펙

TS – training sequence

- Bit tracer나, 오실리스콥같은걸로 봐야하는데, 이건 간략학, 이건 cadence 에서 알아서 하는거라고 보면된다. 이 상태

Time Delta 는 이제 Training sequence 들간의 시간 차에

PERST – pin을 통해서 시그널을 가지고 device 를 0 이면 reset , 1이면 reset이 풀리는거고

UART에서 보면 toggle될때 찍히게 된다.

ROM msg ->

bios에서 한번더 reset을 치고싶어서 P0_PERSTN 1 , enable link 이다.

P0_PERSTN 1 , enable link -> 이거 나오면 바로 init부터 다시한다.

Pcie 에서 단에서 reset 을하는거니까 , base address정보 조차도 다 날라가는거다. Power만 연결되어있는거지, reset은 처음 pcie 부터 다 다시하게된다.

---여기가지가 link layer

그다음은Data layer다.

내가 어떤 특정 패턴이 들어가서 그게 제대로 들어갔는지

SDS를 보면 그전에 L0는 다 되었다. L0 state 면 pcie link적으로 ready가 되었다고 보는거다.

LTSSM

Detect -> polling –> config –> L0 (cmd를 주고받을수있는 pcie ready상태다)

L0 : Pcie 통신이 가능한 상태,

TLP 라는건 transactio packet을 던져서

Config write를 해서 writable한 device인지 파악. Link적으로 준비가 되어도, ㅇ

보통 client 에서는

조금더 pcie

약간의 delay가 약간 있다. 실제적으로 pcie 에서는 아직 ready가 안된상태

requesterID(root complex ID)

completerID(

DeviceID – 에기 BDF정도(lspci)

AckNak도 TLP number마다 붙어있다.

STATUS – CRS(completion 이 ready가 안되었으니 다시 보내) – pcie 스펙에 용어들이 적어놨다.

LeCroy가 독점을 Protocol Analysis 처음에 4억에서 시작했는데 16억이다.

Split tra 에서는 pcie 단에서 는 인식이 되었다는거(lspci 로 확인가능)

Config wirte할수있는건 , config read할수있지만

Pcie cfg 는 접근이 가능하다. 근데 io관련은 불가능

Equalization 이라는건 SI를 좋게하는거다. -> gen3에서 처음생기는건데, 뭉개지면서

Lane loss에 대한 보상을 하기위해서

처음에 봤던거랑 유사하다.

Equal을 할때,

Host가 불안정을 할때, 도 있고

Pcie 가 불안정하면 다같이하는 경우도 있다.

Link

메모리로 세팅을 하기위해서

1.2.3 PCIe Configuration 메모리 enable 도 해야하고

00정보에서는 device 하고 vendor ID가 들어가게되어있다. Class code , command 를 확인을 하게된다. Base address가 여러가지 있고,

Base address reg 는 storage장치에서 쓰이는 address정보 이다. 그걸 확인하는 config reg가,

Host는 막 던지고 계속 확인하고, class code – 이건 nvme 를 연결 하기위한 작업이다. 여기서 ssd 드라이브라고 최초로 아는지점이다. Split Tra이다.

그 다음으로 필요한게, 메모리 방식,

Register command

IO space – Ethernet 장치들 옛날 장치들같은거….

UR이라고 지원을 안하는거 unsorted request라고 보낸다.

여기까지 하는거

Cfg,다음에 MEM – 메모리 커맨드가 나온다.

여기까지하고 이제 nvme로 갈수가 있다.

Tracer는 중간에 interposer 가 있고 거기서 중간 신호를 뽑는다.

Nvme 쪽에서

Cofgre가 다 되면, Base address르 ㄹ봄

NVMe Config가 있다. – nvme config reg가 있다.

Control Config (CC) – device 를 enable 하는거 EN - 0으로 가야한다.

Adm Sub Q,

LeCroy가 pcie는 잘햇는데, nvme는 약간 해석이 이상하다.

memmory통신은 뭘로하지?(memory 를 어떻게 쓰자는거에대한 규약)

nccm 이라고 nvme control memory 영역 device가 가지고 있는거니까

이거를 읽어 보려고 했을때,

CC – 1

CSTS – 1 은 nvme 0가 잡힐것이다. Identify 가 안되었기에, 아직 모른다.

setFeature 를 날려서 OS까지 drive

16개 queue까지 만든다.

Doorbell은 interrupt방식이다.

동현's note