[Computer Architecture] 명령어 사이클

명령어 사이클?

CPU가 하나의 명령어를 실행하는 데 필요한 전체 처리 과정

PC?

Program Counter의 약자로, 다음에 실행할 명령어의 주소를 저장

MAR?

Memory Address Register의 약자로, 다음에 접근할 메모리의 주소를 임시 저장

MBR?

Memory Buffer Register의 약자로, 메모리에 저장되거나 메모리로부터 읽어온 데이터를 임시 저장

IR?

Instruction Register의 약자로, 현재 실행중인 명령어를 저장

Interrupt?

프로그램의 실행 중, 예외상황이 발생하여 처리가 필요한 경우에 CPU에게 알려 처리할 수 있도록 하는 것

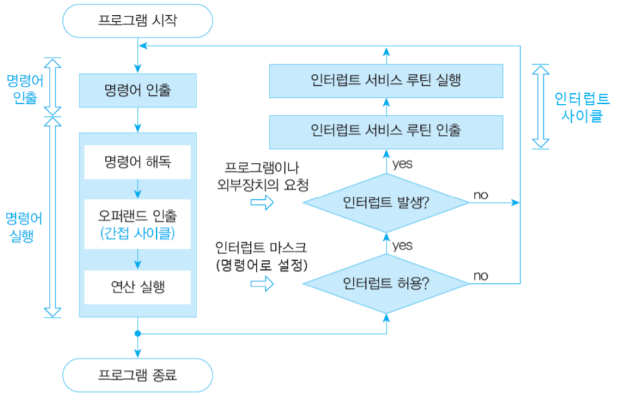

명령어 사이클

명령어 사이클은 CPU가 하나의 명령어를 실행하는 데 필요한 전체 처리 과정으로서, CPU로부터 명령어를 읽어오는 단계인 인출 사이클(Fetch Cycle) 과 명령어를 실행하는 단계인 실행 사이클(Execution Cycle) 로 분리할 수 있습니다.

인출 사이클(Fetch Cycle)

-

PC에 저장된 명령어 주소를 MAR에 저장

-

MAR에 저장된 주소의 값을 MBR에 저장, PC가 다음 명령어 주소를 가리키도록 +1

-

MBR의 값을 IR로 이동

실행 사이클(Execution Cycle)

- IR의 인출된 명령어를 해독

- Opcode(명령 코드) 해독: 인출한 명령어의 Opcode를 해독해 동작을 구현하는 회로로 신호 전송

- Operand(피연산자) 해독: 주소 지정 방식에 따라 Operand에 저장된 값을 통해 유효 주소를 얻는 과정 (= 간접 사이클)

- 명령어 실행에 필요한 CPU 제어 신호를 발생시켜 실제 명령어를 실행

인터럽트 사이클(Interrupt Cycle)

인터럽트 발생 시 처리를 위한 단계로 처리가 완료되면 인출 사이클을 진행