Paging

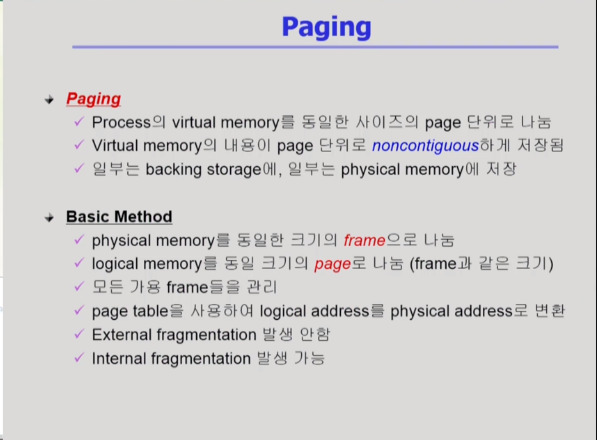

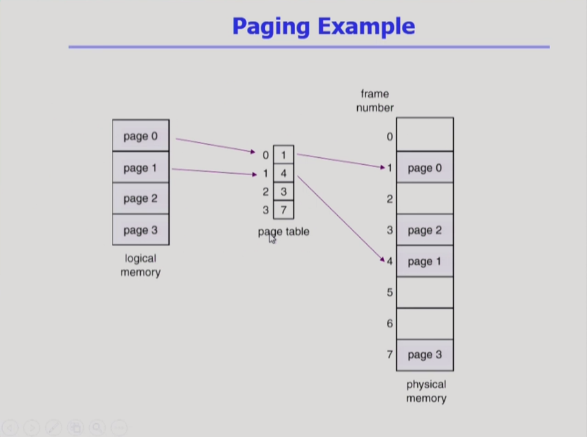

프로그램을 구성하는 논리적인 메모리(logical memory)를 동일한 크기(page)로 잘라서 각각의 page별로 물리적인 메모리의 비어있는 곳에 올라간다.

-

주소변환을 위해서

page table사용- page table은 논리적 메모리의 개수만큼 entry가 존재한다.

- 배열이라는게 실제로 사용될 때 table로 쓰이는데, 각각이 entry가 된다. 여기선 어떤물리적 메모리 주소 가야하는지 적혀있음.

- page table은 논리적 메모리의 개수만큼 entry가 존재한다.

-

page table은 순차적 검색 x => entry의 크기가 미리 정해져있기 때문에

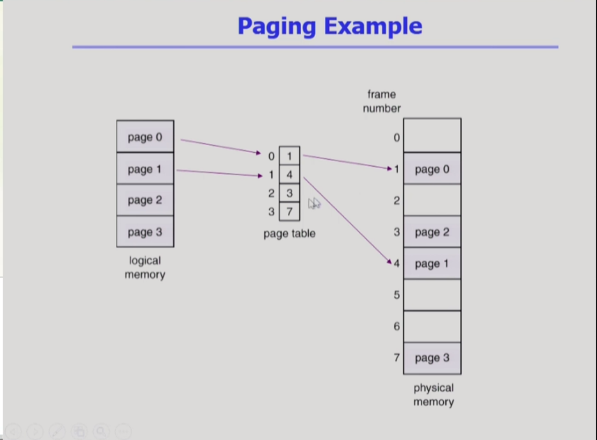

Address Translation Architecture

1) cpu가 논리적인 주소를 주게 되면,

이거를 물리적인 메모리 주소로 바꿔야 되는데

2) paging 기법에서는 주소변환을 할 때 page table을 이용한다.

3) p : 페이지 번호

d : 페이지 내에서 얼만큼 떨어져있는지 나타내는 offset

4) 논리적인 page 번호에 해당하는 entry를 page table의 위에서 p번째 찾아가면

5) f라는 페이지 프레임 번호가 나타난다.

6) 그럼 논리적 주소를 => 물리적 주소로 바꾸게 됨.

논리적인 페이지번호를, 물리적인 프레임 전호를 위에서 몇번째 번호인지로 바꿔주면

7) 주소 변환 끝.

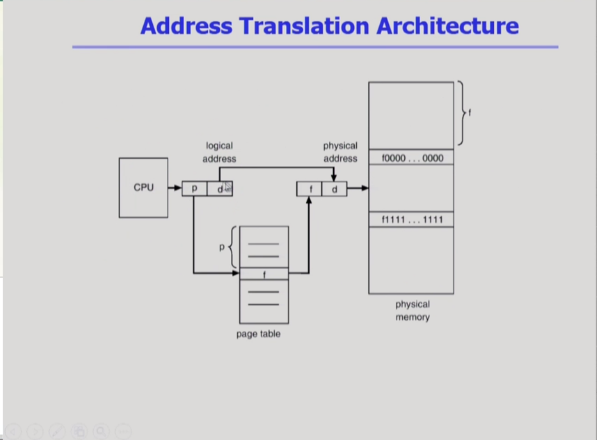

Paging Example

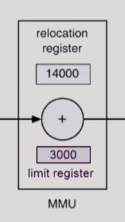

기본적인 MMU 기법에서는 레지스터 두개로 주소 변환

레지스터 : CPU안에 들어가 있는 아주 빠른 장치.

- 보통 Page의 크기는 4Kbyte

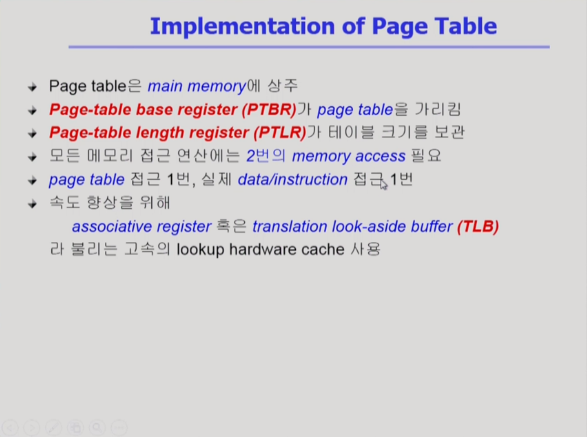

Implementation of Page Table

- 프로그램마다

page table이 별도로 있어야 한다.page table의 용량이 너무 크다.

- 레지스터에 못넣음

- 메모리 접근을 위한 변환을 하드디스크에 저장할 수도 없음.

- 캐시 메모리에 넣기에도 용량이 너무 큼.

=>page table을메모리에 집어넣자!

메모리에 접근하기 위해서 주소변환을 해야하는데 , 주소변환을 하려면 page table에 접근해야 하고, page table이 또 메모리에 있기 때문에

=> 메모리에 2번 접근이 필요함

- 비용이 상당히 큼.

- 시간이 두배로 걸리니까. 기본적인 MMU기법에서 레지스터 2개가 paging 기법에서는 어떻게 사용되는가?

- PTBR (Page-table base register)

- PTLR (Page-table length register)

PTBR (Page-table base register)

메모리 상에 page table이 어디 있는지 시작위치

PTLR (Page-table length register)

page table의 길이

속도 향상을 위해, 하드웨어 사용

associative register로 구성되는TLB(일종의 cache)- 메인메모리하고 cpu 사이에 존재하는 주소변환 해주는 계층임.

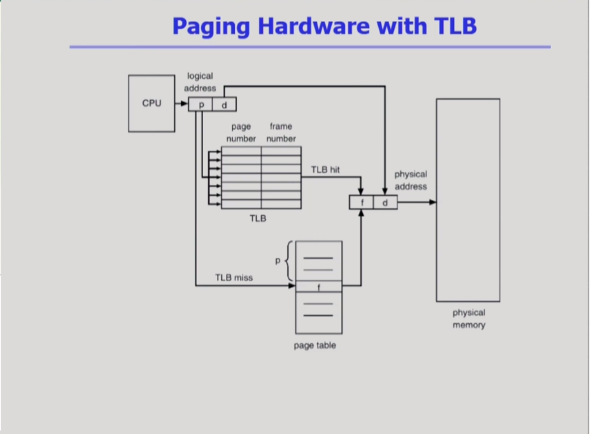

Paging Hardware with TLB

사실은 이 page table이 physical memory 안에 있음.

원래 original paging 기법

- cpu가 주는 logical address에 대해서

- physical memory 상에 존재하는 page table을 통해서 주소변환을 하고

- 변환된 주소로 physical memory에 접근한다.

속도 개선 위해서 TLB라는 별도의 하드웨어를 둠

정보1)

메인 메모리(physical memory) 윗단에 cache memory가 있음 !

- cacha 메모리는 운영체제에선 감추어진 계층임.

- 메인메모리에서 빈번히 사용되는 data를 cache memory에 저장해서 cpu로부터 더 빨리 접근할 수 있게 한다.

주소변환을 위한 별도의 cache memory를 두는 것 => TLB

- page table에서 빈번히 참조되는 entry를 caching 하고 있음.

- 메인 메모리보다 접근 속도가 빠른 하드웨어로 구성

따라서, cpu가 논리적인 주소를 주게 되면 메모리(physical memory) 상에 있는 page table에 접근하기 전에 TLB를 먼저 검색한다.

- 혹시, TLB에 저장되어있는 정보를 이용해서 주소 변환이 가능한지 check

- 가능하다면, 주소변환을 해서 physical memory에 바로 접근가능

주의)

빈번히 참조되는 entry 몇개만을 TLB에 담고있는 것임 !

- 가능하다면, 주소변환을 해서 physical memory에 바로 접근가능

page table에서는 주소 변환을 할 때,

- page 번호가 p이면 위에서부터 p번째 entry를 가면 주소 변환이 됐음. f라는 page 프레임 번호가 나옴.

TLB는 page table 내용을 전부 가지고 있지 않기 때문에,

- 논리적인 page번호 p하고 물리적인 page f를 쌍으로 가지고 있어야 한다.

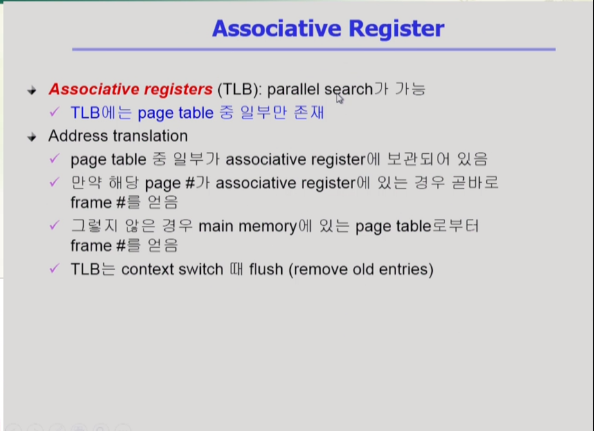

주소 변환을 위해서 TLB의 특정 항목을 검색하는 것이 아니라, 전체를 검색해야 한다.

- 위에서부터 전체 항목에 대해서 p가 있는지 확인.

- 전체를 다 찾아보는데 시간이 오래 걸린다

=>parallel search가 가능한 병렬적 탐색이 가능한 Associative Register를 이용한다.

Associative Register

각 프로세스마다 page table, TLB가 다르기 때문에 프로세스가 바뀌는 context-switch 때 flush를 해서 모든 엔트리를 비워야 한다.

- 프로세스마다 주소변환정보가 다르다는 뜻.

Effective Access Time

실제로 메모리에 접근하는 시간을 얼마나 될까?

-

TLB에 접근하는 시간을

입실론(ε, epsilon) -

메모리에 접근하는 시간 1

=> TLB 접근시간 < 메모리 접근시간 -

TLB로부터 주소 변환이 되는 비율을

알파라고 하자.

실제로 메모리에 접근하는 시간은?

결과적으로,

- TLB에서 주소변환이 되는 비율 알파가 굉장히 높다.

- 입실론은 굉장히 작은 값.

Page table만 있을 때는 값이 2이고, (메모리 접근 2번 하니까. )

TLB도 있을 때는 2 + ε - α이 된다.

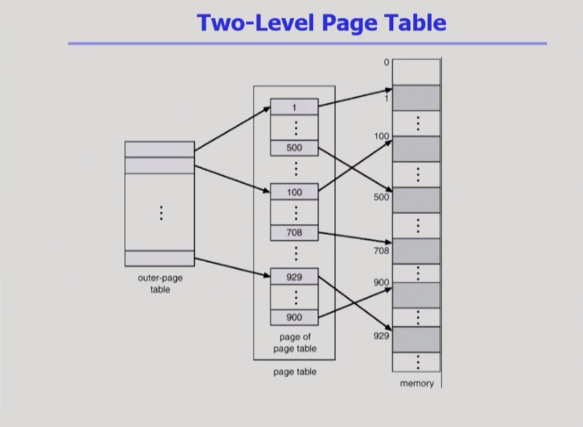

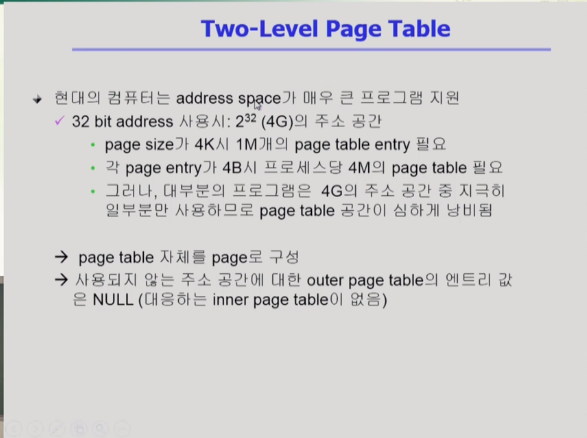

Two-Level Page Table

2단계 Page Table임.

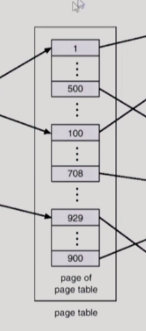

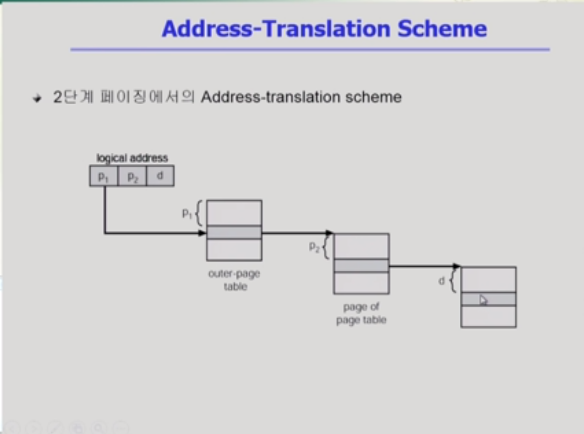

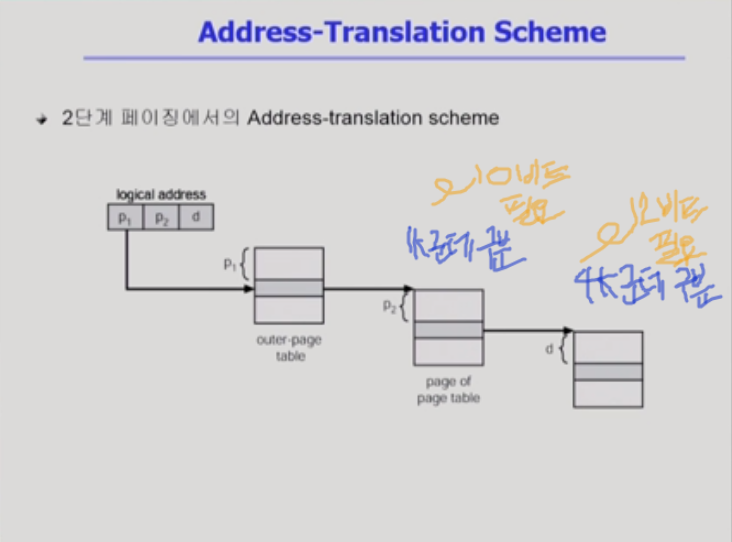

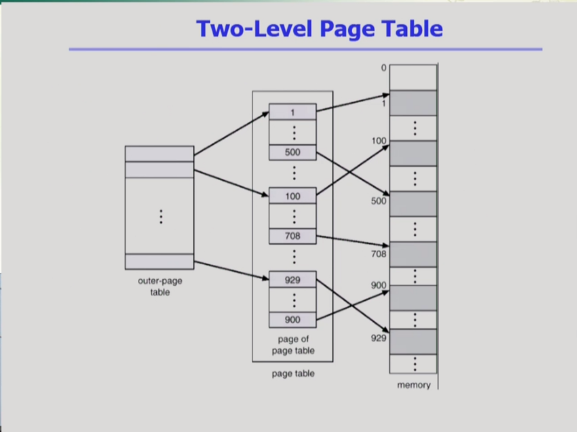

cpu가 논리적 주소를 주게 되면 ~ page table을 두단계 거쳐서 주소 변환을 하고 실제 메모리 접근을 한다.

안쪽 page table

바깥쪽 page table

메모리 접근

2단계 page table을 써야 하는 이유는?

- 속도 ? : 시간은 더 걸림. 2번 접근하니까

- 공간 : 공간이 줄어든다.

- 현대 컴퓨터는 메모리 주소 체계가 굉장히 큼.

Address-Translation Scheme

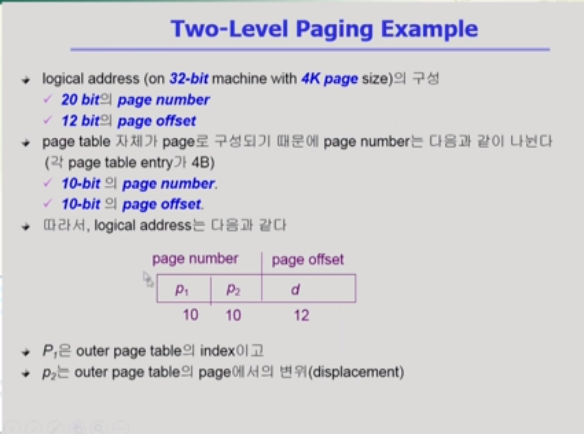

Two-Level Paging Example

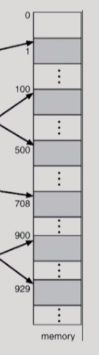

- 바깥쪽 page table은 전체 논리적 메모리 크기만큼 만들어진다.

- 사용안하는 주소 공간에 대해서는 null이 되어있다.

- 안쪽 page table은 실제 사용하는 주소만 만든다.

=> 메모리 공간 효과적(사용안되는 주소 공간 엄청 많음.)