프로세서 구조

8086의 경우 20비트 주소 버스, 16비트 데이터 버스를 사용한다.

데이터 버스의 크기는 판독과 기록 사이클의 횟수를 결정한다. ex) 32비트로 된 자료를 읽기 위해서는 16비트 데이터 버스를 사용하는 8086에서는 2회를 읽어야 한다.

16비트 인텔 프로세서

1단어 = 2byte

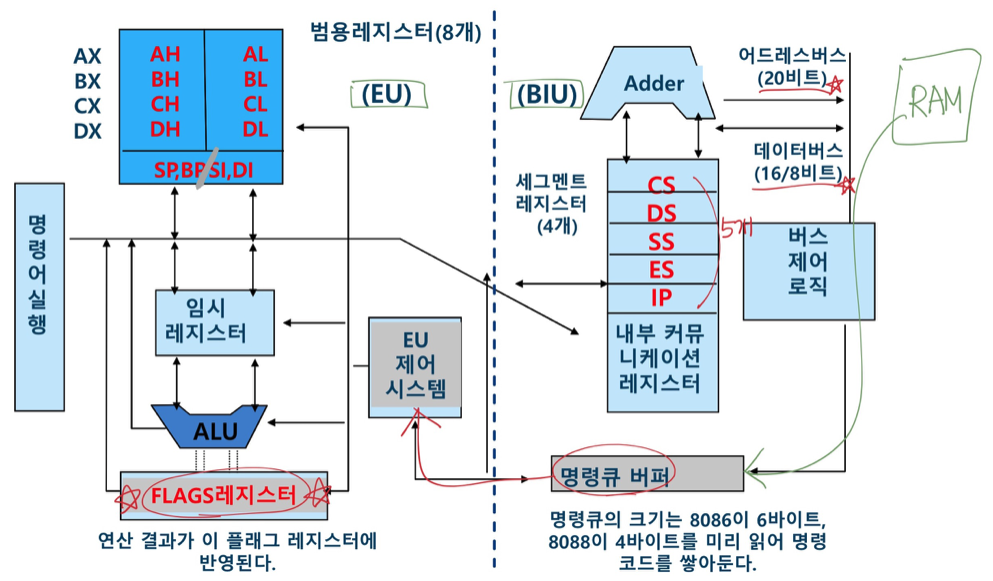

EU(Execution Unit) : 명령어 실행 장치

- 명령을 실행하고 연산

- 8개의 범용 레지스터

- 산술 논리 연산 장치(ALU)

- 플래그(Flags) 레지스터

BIU(Bus Interface Unit) : 버스 인터페이스 장치

- 명령어를 인출(Fetch)

- 기억장치나 입출력장치로부터 데이터를 읽어오거나 출력(RAM과 연결)

- 4개의 세그먼트 레지스터(CS, DS, SS, ES)

- 명령어 포인터(IP)

- 유효 주소 계산을 위한 가산기(Adder)

- 명령어 큐 : 실행할 명령어를 기억 장치로부터 가져와 임시로 저장하는 버퍼

내부버스 : 프로세서 내부에 각 부분 사이의 자료를 전달해주는 버스

레지스터의 종류

데이터 레지스터(4개) AX, BX, CX, DX : 일시적인 결과 기록

포인터 레지스터(3개) SP, BP, IP : 스택 포인터와 베이스 포인터

인덱스 레지스터(2개) SI, DI : 데이터의 주소 저장

플래그 레지스터(1개) Flags R : 연산 결과의 정보 저장

세그먼트 레지스터(4개) CS, DS, SS, ES : 세그먼트의 시작 주소 저장

세그먼트 레지스터는 세그먼트의 시작 주소를 가리킨다. (코드 세그먼트, 데이터 세그먼트, 스택 세그먼트, 여분의 데이터 세그먼트)

프로세스의 개념

작업(job) : 실행 프로그램과 이에 필요한 입력 데이터의 묶음. 컴퓨터에 실행 의로되기 전의 상태

프로세스(process) : 프로그램이 실행되기 위해서는 반드시 실행되기 전에 주기억장치에 저장되어야 한다. 커널에 등록된 작업으로 운영체제에 의해 관리된다.

플래그 레지스터의 구성

프로그램을 실행할 때 앞의 연산 결과가 음수인지 양수인지, 컴퓨터 사용자가 일반인지 관리자인지 등의 정보를 16비트 크기의 상태 레지스터에 기록되고 이것에 기록되는 각 비트들을 플래그라고 한다.

8086의 9가지 플래그

수치 연산과 논리 연산의 결과에 의한 CPU의 상태를 나타내는 상태 플래그 : CF, PF, AF, ZF, SF, OF

CPU 동작을 변화하기 위한 제어 플래그 : TF, IF, DF

16 인텔 프로세서의 버스 크기

데이터 버스(8086에서는 16bits)

데이터 버스의 크기는 판독과 기록 사이클의 횟수, WORD(데이터 양)를 결정한다.

(32비트로 된 자료를 판독하거나 기록할 때 16비트 데이터 버스일 경우 2회 읽는다.)

주소 버스(8086에서는 20bits)

주소 버스의 크기는 최대 기억 장치 주소를 결정한다.

2^20 = 1,048,576(1MB) 주소를 지정할 수 있다.

명령어의 실행 단계

명령어 인출(IP+2) - 명령어 해독 - 데이터 인출 - 실행 사이클

명령어의 길이

8비트로 이루어진 명령어를 예로 들어보면, 주소 지정 방식이 4가지, 레지스터가 2개가 있다면 👉🏻 주소 지정에 2비트, 레지스터에 1비트가 필요하다. (3bit)

명령어는 8bit - 3bit = 5bit, 2^5(32)개만 만들 수 있다.

명령어의 길이는 1. 레지스터의 개수 2. 주소 지정 방식의 종류 3. 명령어의 종류에 따라 결정된다.

명령어의 형태

명령어 코드(5bit) + 오퍼랜드(3bit) = 8bit로 구성된다. 오퍼랜드에는 주소지정방식과 레지스터가 표현된다.

오퍼랜드의 첫 2bit에는

00 직접 주소지정방식

01 베이스 주소지정방식

10 인덱스 주소지정방식

11 베이스 인덱스 주소지정방식

이 포함되고 남은 1bit에는

1 레지스터 A (AX)

0 레지스터 B (BX)

가 포함된다.

8086 계열 어셈블리어 명령어 크기는 1단어(2바이트)로 기본 구성되며 최대 3단어(6바이트)까지 확장 가능하다.

Q. 다음과 같은 조건을 만족하는 명령어를 만들고자 할 때, 명령어의 길이가 최소한 몇 비트가 되어야 하는지

명령어 코드의 종류 64개2^6 = 6비트

주소 지정방식 8개2^3 = 3비트

레지스터 16개2^4 = 4비트

데이터 크기 코드 3개2비트(기본 2비트)

A. 6 + 3 + 4 + 2 = 15비트

기억 장치

8086 프로세서와 함께 동작되는 기억장치는 주소가 물리 주소로 붙여지고 20비트의 주소 버스를 이용한다. (=2^20B=1MB)

이때 마지막 주소는 FFFFFH이다.

8086 프로세서에서는 메모리가 짝수 주소 뱅크(좌측 바이트)와 홀수 주소 뱅크(우측 바이트)로 구성된다. (BIU에서 주소 자동으로 처리)

주소 지정에 의한 액세스 효율은 짝수 + 홀수 조합의 효율이 좋다.

데이터 기록 시 일반적인 규칙

8086에서는 기억 장치에 세그먼트 단위로 필요한 데이터나 프로그램을 저장한다. 16비트 단위로 작업하고 처리할 데이터의 크기에 따라서 소요되는 사이클 시간이 다르다.

기억 장소 주소는 바이트 단위로 되어 있다. 바이트 주소는 1씩 증가하고, 짝수와 홀수의 값을 가진다.

단어 주소는 2씩 증가하며 짝수의 값만을 가진다.

프로세서가 N번지의 1단어에 접근하면 자동으로 N, N+1 바이트에 접근한다.

N번지의 긴 단어에 접근하면 4개의 바이트 N, N+1, N+2, N+3 에 접근하게 된다.

기억 장치에서의 단어 배열은 기억장치 N번지에 2A, N+1번지에 51이 들어있다고 가정할 때, 레지스터에는 51 2A의 순서로 들어간다.

즉 N번지는 단어의 하위 바이트고 N+1번지는 단어의 상위 바이트가 된다. 레지스터에서 기억 장치로 데이터를 쓰거나 읽어올 때는 그 단어의 하위 바이트를 먼저 기록하고 후에 상위 바이트를 기록한다.

레지스터의 개념

레지스터는 데이터를 빠르게 읽고 기록할 수 있는 기억 장치로 중앙처리장치 내에 있는 임시 기억장치이다.

명령어의 임시 보관이나 데이터의 일시적인 중간 결과를 보관한다.

8086에서는 16비트 레지스터 14개가 존재한다.(데이터 레지스터 4개, 인덱스 레지스터 2개, 포인트 레지스터 3개, 세그먼트 레지스터 4개, 플래그 레지스터 1개)

여기서 데이터 레지스터는 2개로 분할하여 사용할 수 있고 포인터, 인덱스, 세그먼트 레지스터는 16비트로만 사용이 가능하다.

데이터 레지스터

각종 데이터 처리 시 일시적인 결과를 기록하기 위해 사용한다. 프로그래머가 명령 중에 자유롭게 지정 가능한 범용 레지스터이다.

상위, 하위 레지스터를 각각 엑세스 할 수 있다.

AX(AL, AH) : Accumulator

- 산술 논리 연산의 결과를 저장

BX(BL, BH) : Base

- 간접 주소 지정 시 베이스 주소를 가리키는 레지스터로 사용

CX(CL, CH) : Counter

- string이나 loop에서 반복 횟수를 카운트하는 레지스터

DX(DL, DH) : Data

- 입출력 주소 저장에 사용되며 상위 워드용 데이터 레지스터로 사용되는 보조 어큐물레이터

포인터 레지스터

스택 포인터(SP) : 스택 조작을 위해서 사용하는 레지스터로 프로그램 실행 중에 데이터의 저장 주소를 기억하고 있다.

베이스 포인터(BP) : 기본적으로 스택 영역 내의 주소를 지시하지만 스택 세그먼트 SS영역 내에 배치한 데이터에 대한 베이스 주소를 지시한다.

인덱스 레지스터

데이터의 주소를 나타내기 위해 사용한다.

SI(Source index register) : 연산 항 소스, 소스 데이터 지정에 사용

DI(Destination index register) : 연산 항의 처리 대상, 즉 목적 항의 데이터를 나타내는데 사용

플래그 레지스터의 구성

CF(Carry Flag) : 최상위 비트에 자리올림/내림이 발생하면 1로 세팅. 부호 없는 정수에 대한 오버플로우를 나타낸다.

PF(Parity Flag) : 최하위 비트가 짝수 패리티인 경우에 세트 되고, 홀수의 경우는 클리어(0) 된다. 데이터 전송에 있어 에러 검출에 사용한다.

AF(Auxiliary Carry Flag) : 10진 산술연산(BCD) 명령에 사용하고 하위 니블(4비트)에서 상위 니블로의 자리 올림 또는 상위에서 하위로 자리 내림이 있을 때 1로 세트된다.

ZF(Zero Flag) : 연산 결과가 0으로 되었을 때 1로 세트된다.

SF(Sign Flag) : 연산 결과의 최상위 비트가 1일 때 1로 세트된다. 즉 최상위 비트가 1이면 음수, 0이면 양수를 나타낸다.

OF(Overflow Flag) : 산술 연산 결과의 오버플로우 상태를 표시한다.

DF(Direction Flag) : 문자열 명령에서의 실행 방향을 제어 (1 - 자동 감소 방향, 0 - 자동 증가 방향)

TF(Tramp Flag) : 프로세서를 프로그램 디버그용의 싱글 스텝 모드가 가능하도록 세팅

IF(Interrupt-enable Flag) : 외부 인터럽트가 가능 또는 불가능을 나타내는 비트

세그먼트 레지스터

CS(코드 세그먼트) : 프로그램의 명령 코드를 포함한다. CS 레지스터는 이 세그먼트의 선두 주소이다.

DS(데이터 세그먼트) : 프로그램을 위한 데이터를 저장하고 있으며 DS 레지스터는 이 세그먼트의 선두 주소를 가지고 있다.

ES(엑스트라 세그먼트) : 여분의 데이터 세그먼트이며 주로 스트링 명령을 수행할 때 사용한다. ES 레지스터가 이 세그먼트의 선두 주소이다.

SS(스택 세그먼트) : 인터럽트와 서브루틴의 반환 주소를 저장하는데 사용한다. SS 레지스터는 이 세그먼트의 선두 주소이다.

하나의 세그먼트는 16비트이므로 하나의 세그먼트 기억 용량은 64KB(2^16)이다.

하나의 프로세스를 처리하기 위해 필요한 최대 기억 용량은 4 * 64KB = 2^2 * 2^16 = 2^18Byte이다. (4가지 종류의 세그먼트 레지스터가 있기 때문에 4를 곱한다.)

👉🏻 주소 버스 크기 : 20비트, 데이터 버스 크기 : 16비트

👉🏻 IP, CS, DS, SS, ES : 16비트

👉🏻 주기억 장치 용량 1MB(2^20), 한 사이클 시간에 2^20가지 주소 전달

논리 주소와 물리 주소의 관계

실제 주소 = CS 값(세그먼트 레지스터 값 * 16 = 세그먼트 물리 번지) + 오프셋 값

명령어 포인터의 동작

명령어 포인터(IP)는 프로그램의 실행 순서를 조절하기 위해 명령어의 주소를 기억하는 레지스터 CS와 쌍이 되어 실제 주소를 만든다.

CS는 직접 엑세스 불가한 레지스터이다.

직접 수정이 가능한 플래그에는 CF, DF, IF가 있다.

Q. CS의 값이 1B00h이며, IP의 값은 00FFh이다. 이때의 실제 물리주소 번지는?

A. 1B00h + 00FFh = 1B0FFh