TIL을 다시 적기 시작한다...

2주차를 진행하다가 음식을 잘못먹고 급성장염으로 몇일간 아프면서 TIL도 같이 중단됐었다. 그리고 그 사이에 벌써 3주차로 넘어왔다. 2주차 내용은 아직 많이 쓰지도 못했는데 말이다.

그래도 다시 써보고자 3주차부터 다시 쓰려고 한다. 2주차 나머지 내용은 나중에 시간이 있을때 별도로 작성하는 걸로 할 예정이다.

오늘로 3주차 3일째이다. 월요일 오후부터 시작해서 3일차이다. 오늘까지 기본적인 이론을 공부했다. 그 내용들을 조금 여기에 정리해고자 한다.

가장 초기의 OS에서 page allocation 방식은 contiguous allocation(연속할당) 방식이었고, 이런 방식은 치명적인 외부 단편화 문제를 발생시켰다.

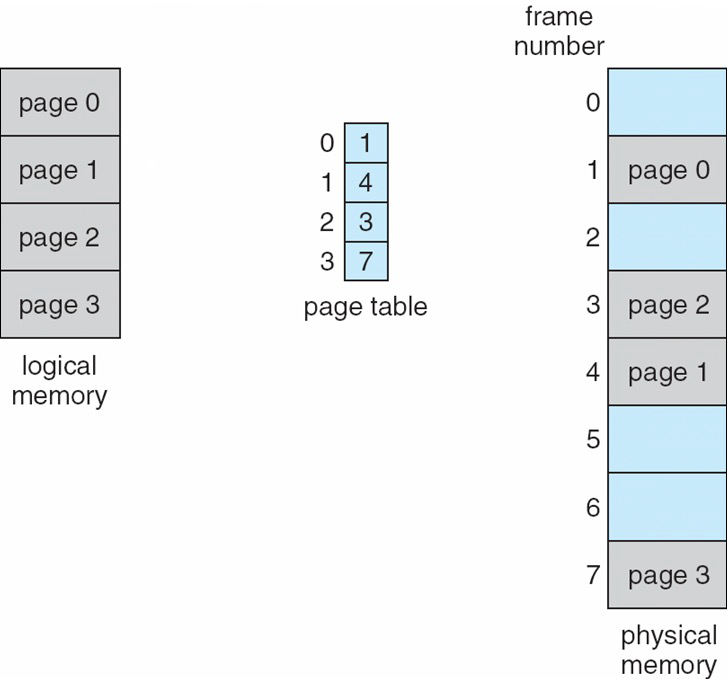

이러한 문제를 잡기 위해서 메모리를 동일한 크기인 page로 쪼개는 방법이 나왔다. page를 사용하면서 메모리를 100% 만큼으로 사용할 수 있게 되었는데, physical memory에서 여기저기 퍼져있기 때문에 프로그램이 수행하는데 지장이 없도록 도와줘야 한다.

paging 이란 간단히 말해 논리 주소 ( = 가상 주소)는 연속적으로 할당하나 물리 주소를 비 연속적으로 할당하는 것이다.

논리 주소에서 고정적 단위를 page라고 한다.

물리 주소에서 고정적 단위를 fram이라고 한다.

이런 paging을 도와주는게 바로 page table이다.(아래의 그림 참조)

만일 논리 메모리 상에서

page0, page1에는 카카오톡 프로그램이 할당되고

page2, page3에는 네이버 프로그램이 할당됐다고 한다면,

물리 메모리에서 실행순서는 0-2-1-3 으로 실행되니까 이상하게 실행이 될 수 있다.

이런 문제를 해결하고 CPU가 프로그램을 연속적으로 실행시키기 위해서 나온게 page table이다. page table은 어떻게 mapping 됐는지 기록하는 table이다.

page table은 기본적으로 프로세스 마다 하나씩 가지고 있는 테이블이다. 그리고 여러개의 page table entry의 집합이다.

하나의 프로세스는 여러개의 page 로 쪼개져서 각각 대응되는 하나의 frame에서 데이터를 읽어와야 하는데 이를 위해서 page table entry에는 page number와 page offset의 정보와 그외 추가적인 정보들을 담고 있다.

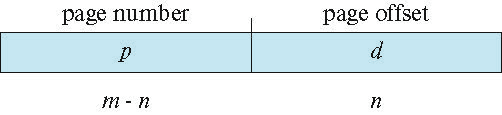

32bit의 프로세서일때라고 가정할때, cpu에서 생성된 bit에서 page를 선택하는 bit는 위의 그림과 같은 format을 따른다.

한번에 CPU가 2^20 만큼의 페이지 번호를 구분할 수 있고, offset으로는 12bit를 이용해서 나타낼 수 있다. 이렇게 두 가지 정보를 조합하여 page table에서 실제 frame의 주소를 확인하고 찾아갈 수 있다.

multi-level page table에 대해서도 간단하게 정리해보자.

page table은 각 프로세스마다 가지고 있으며 프로세스가 많으면 많을 수록 많은 영역을 차지한다는 것이다. page table의 크기를 줄이기 위해서는 어떻게 해야 할까.

1) 가장 간단한 방법은 Page 자체의 크기를 늘리면 된다. 그러면 entry 개수가 줄면서 전체 table의 크기가 줄게된다. 하지만 이런 방식을 사용하면 실제로는 internal fragmentation을 증가시켜 메모리가 낭비된다.

2)segmentation을 하는 방법도 있다.

Code, Stack, Heap을 위한 Page Table을 따로 분리한다.(Heap과 Stack사이 공간을 위한 Page Table이 필요없다)

하지만 이 경우에는 두 가지 문제가 발생할 수 있다.

- Page Table waste (sparsely-used heap space)

- External fragmentation (variable size of Page Table)

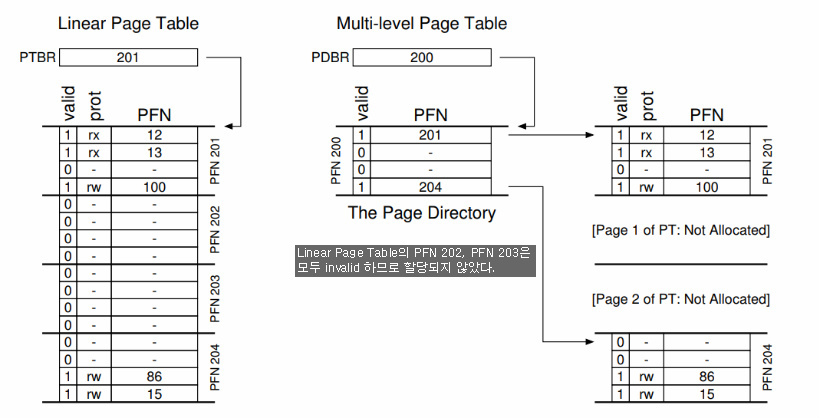

3)Multi-Level Page Table

이 방식은 Page Table을 위한 Page Table을 만드는 것이다. Page Table을 기존의 선형구조가 아니라 Tree 구조로 만드는 것이다. 아래의 그림은 Level 2 로 구성된 Page Table이다.

위 그림에서 PDBR은 Page Directory Base Register로 물리 메모리 공간에 저장되어 있는 Page Directory의 Base 주소를 가진다.

invalid 한 entry를 담은 Page는 memory에 할당되지 않아서 효율적으로 관리할 수 있다.

물론 단점도 존재한다.

1) TLB Miss가 났을 경우 두번의 Memory 접근이 필요하다. Page Directory로 접근하고 거기서 얻어온 Page Table Entry정보로 다시 접근을 해야 한다.

2) Complexity 가 증가한다. Page Table의 검색이 더 복잡해진다.

Page Table에 대한 기본적인 이론 정리는 이렇게 마치고, 우리가 핀토스에서 해야 하는 일은 무엇이기에 이 내용을 다시 공부하고 정리하였는가?

핀토스에서 Virtual Memory 구성을 위해서 해야할 일들이 매우 많이 있는데, 우리가 당장 직면한 것은 바로 supplement page table을 구성하는 것에서부터 시작해야 한다.

다양한 자료를 읽는 것을 통해서 이전까지 userprog에서는 Thread 구조체에 pml4라는 필드가 자동으로 생성되어 프로그램들이 실행이 되었다. level4로 page table이 생성되어서 자동으로 작동했지만, VM 파트로 넘어오면서 해당 테이블은 없어졌다.

가장 처음으로 해야 하는 일은 이 PML4를 대체하는 page table을 생성하고, 이에 대응하는 frame table도 작성하여 제대로 된 위치를 참조하도록 만들 것이다.