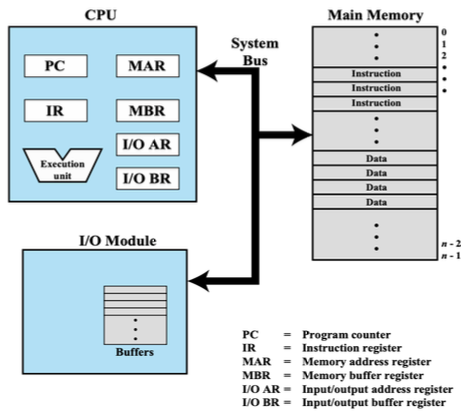

컴퓨터 구성요소

- Processor: 컴퓨터 동작 제어, 데이터 처리, 프로그램 실행

- Main memory: Data와 Program을 저장한다.

- 휘발성이기 때문에 shutdown 되면 메모리가 삭제된다.

- I/O module: 컴퓨터와 외부 환경 간의 데이터 이동을 담당한다.

- 종류: 키보드, 마우스, 모니터, 스피커 등

- System bus: 프로세서, 메인 메모리, I/O 모듈 간의 통신을 제공한다.

* Program Counter: 다음에 실행할 명령어의 주소를 저장한다.

* Instruction Register: 현재 처리 중인 명령을 저장한다. (주소 아님 주의)

* Memory Address Register: 메인 메모리에서 사용할 영역의 주소를 저장한다.

* Memory Buffer Register: 메모리와 교환할 데이터를 저장한다.

* I/O Address Register: I/O 모듈에서 사용할 영역의 주소를 저장한다.

* I/O Buffer Register: I/O 모듈과 교환할 데이터를 저장한다.

Instructions

- Program: instruction과 data의 집합

- 종류

- 프로세서와 메모리 간의 데이터 전송

- 프로세서와 I/O 모듈 간의 데이터 전송

- 산술 및 논리 연산과 같은 데이터 처리

- 명령어 실행 순서 제어 (프로세서 내에서 처리 가능)

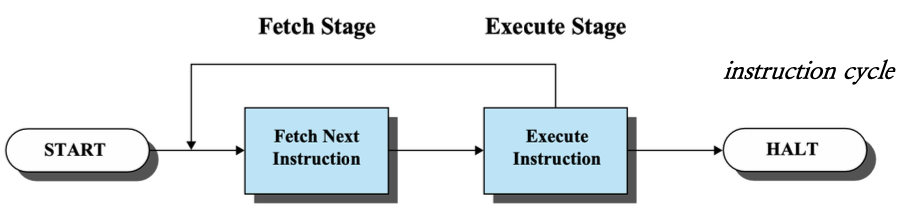

- 명령어 수행 과정

1. Fetch Stage: 프로세서가 메모리로부터 명령어를 읽어서 IR에 저장한다.

2. Execution Stage: 프로세서가 명령어를 수행한다.Fetch Stage

1. MAR <- PC, PC++

2. MAR에 저장된 주소를 통해 메모리에서 명령어를 읽고 MBR에 저장한다.

3. IR <- MBRExecution Stage (Read)

1. IR의 연산코드를 확인해 명령어 종류를 분석한다.

2. MAR <- IR의 주소 부분

3. MAR에 저장된 주소를 통해 메모리에서 데이터를 읽고 MBR에 저장한다.

4. AC(Accumulator) <- MBRExecution Stage (AC 변경)

1. IR의 연산코드를 확인해 명령어 종류를 분석한다.

2. MAR <- IR의 주소 부분

3. MAR에 저장된 주소를 통해 메모리에서 데이터를 읽고 MBR에 저장한다.

4. AC <- AC + MBRExecution Stage (Write)

1. IR의 연산코드를 확인해 명령어 종류를 분석한다.

2. MAR <- IR의 주소 부분, MBR <- AC

3. MAR에 저장된 메모리 주소에 MBR을 저장한다.

- Program Status Word

- Condition Codes(Flags): 연산 결과를 저장한다.

- 종류: Zero, Carry, Overflow, Sign

- Interrupt enable/disable: 인터럽트 허용/비허용 상태

- enable: 프로세서가 외부 이벤트나 하드웨어 요청을 받아들여 실행 중이던 프로세스의 처리를 중단시킬 수 있다.

- disable: 프로세서가 인터럽트를 무시하고 현재 실행 중인 작업을 계속한다.

- Supervisor/user mode: 프로세스가 실행 중인 모드

- 모드에 따라서 수행 가능한 명령과 접근 가능한 시스템 자원이 달라진다.

- Condition Codes(Flags): 연산 결과를 저장한다.

Interrupt

- 프로세서의 효율 향상을 위해 제공된다.

- 종류

- Program: 프로그램을 실행하다가 오류나 예외 상황에 직면했을 때 발생한다.

- 프로그램 자체의 문제가 아니다.

- 예) 산술연산 오버플로우, 0으로 나누기, 잘못된 메모리 접근, 불법적 기계 명령어 수행 시도, 명령어의 명령코드 오류 등

- Timer: 프로세서 내의 타이머에 의해 발생한다.

- I/O: I/O Controller에 의해 발생한다.

- Hardware failure: 하드웨어 결함에 의해 발생한다.

- Program: 프로그램을 실행하다가 오류나 예외 상황에 직면했을 때 발생한다.

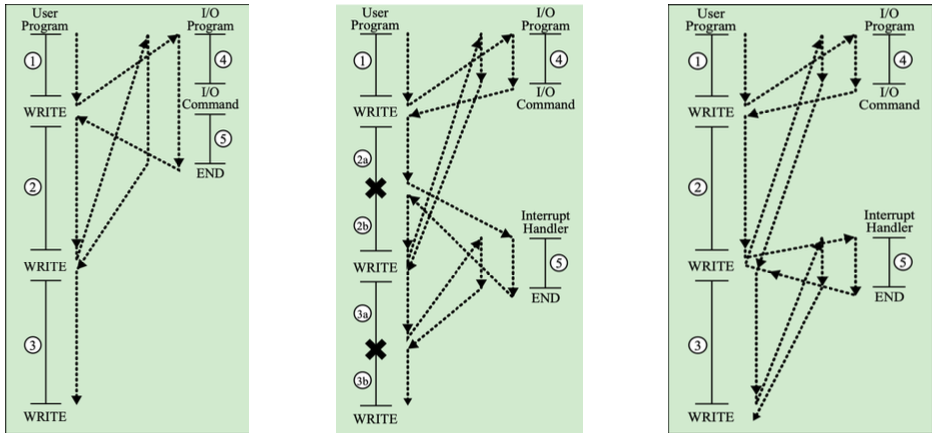

- I/O interrupt

- I/O 모듈은 프로세서보다 훨씬 느리다.

- 인터럽트 X: 프로세서는 입출력 작업이 끝날 때까지 동작을 멈춘다.

- 인터럽트 O & 짧은 입출력 대기: 입출력 작업이 처리되는 동안 프로세서는 다른 명령어를 수행하고, 입출력 명령이 끝나면 인터럽트가 발생하면서 OS가 입출력 연산을 마무리한다.

- 인터럽트 O & 긴 입출력 대기: 하나의 입출력 작업이 끝나기 전에 또 다른 입출력 명령을 만난다면 프로세서는 어쩔 수 없이 대기해야 한다.

- 인터럽트는 입출력 작업이 완료된 후 5번 명령어를 실행하기 전에 발생한다.

- 인터럽트가 입출력 작업의 종료를 알리는 것은 맞지만 현재 프로세스의 입출력 작업 종료는 아니다.

- 4, 5번 명령어는 OS 기능이다.

- Interrupt Handler: OS 기능으로 인터럽트가 발생한 상황에 따라 적절한 처리를 한다.

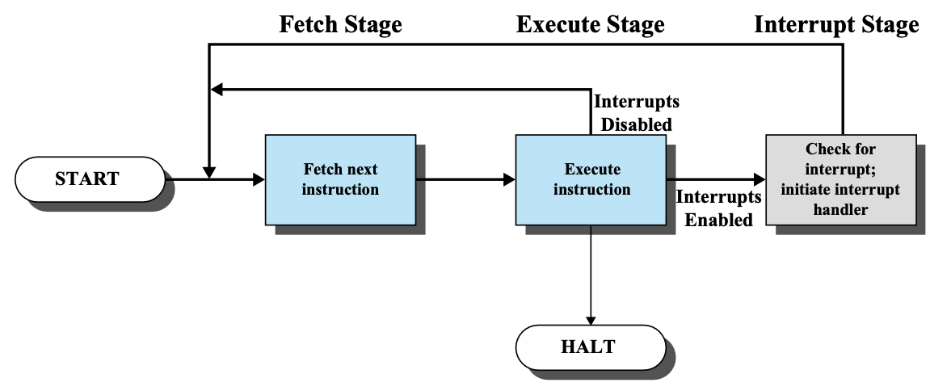

- Instruction Cycle

- 인터럽트가 발생하면 수행 중이던 명령어의 Execute Stage가 끝나고, Interrupt Stage에서 인터럽트가 발생했음을 검사하여 확인한 후에 비로소 인터럽트가 처리된다.

* Fetch Stage에서 PC 값이 바뀌기 때문에 Execute Stage가 끝나기 전에 인터럽트 처리를 하면, 해당 명령어를 수행하지 못하는 상황이 발생한다.

* 인터럽트 발생을 확인한 후에야 원래 처리하던 프로그램의 수행이 중단된다. - PSW의 인터럽트 허용 상태에 따라 Interrupt Stage 실행 여부가 달라진다.

- Interrupt Stage가 끝나면 Interrupt Handler가 실행되거나 이전 Fetch Stage에서 PC에 저장된 명령어를 실행하는데 그 명령어는 원래 실행하던 프로그램의 명령어가 아닐 수 있다.

- 인터럽트가 발생하면 수행 중이던 명령어의 Execute Stage가 끝나고, Interrupt Stage에서 인터럽트가 발생했음을 검사하여 확인한 후에 비로소 인터럽트가 처리된다.

- 인터럽트 처리 과정

- 하드웨어

- 인터럽트를 발생시킨다.

- 프로세서가 현재 처리 중이던 명령어의 Execute Stage 를 완료한다.

- 프로세서가 인터럽트 확인 신호를 전송한다.

- 프로세서가 PSW와 PC를 메인 메모리 상의 컨트롤 스택에 저장한다.

- 하드웨어 차원에서 PSW와 PC를 저장하는 이유: OS(소프트웨어)가 실행되면 PC에 다음에 실행할 OS의 명령어가 저장되므로 원래 수행하고 있던 프로세스의 상태를 복구할 수 없다.

- 프로세서가 Interrupt Handler의 주소 값을 PC에 저장한다.

- 소프트웨어

- 프로세스의 나머지 상태 정보를 컨트롤 스택에 저장한다.

- 인터럽트를 처리한다.

- PSW, PC를 제외한 프로세스의 상태 정보를 복구한다.

- PSW, PC를 복구한다.

- PC, PSW를 미리 복구하면 직후에 PC에 저장된 명령어를 수행하므로 프로세스의 복구 작업이 마무리 될 수 없기에 마지막에 복구한다.

- 하드웨어

메모리 계층 구조

- 메모리 특성: 저장 용량, 접근 속도, 비용

- 용량이 클 수록, 비트 당 비용이 낮아진다.

- 용량이 클 수록, 접근 시간이 길어진다.

- 접근 속도가 빠를 수록, 비트 당 비용이 높아진다.

- 계층 구조

- Top: Inboard memory - Register > Cache > Main memory

- Mid: Outboard memory - Magnetic disk(Hard disk)

- Bottom: Off-line storage - Magnetic tape

- Bottom -> Top: 비트 당 비용 증가, 용량 감소, 접근 속도 증가, 프로세서의 메모리 접근 증가

- Top -> Bottom: 비트 당 비용 감소, 용량 증가, 접근 속도 감소, 프로세서의 메모리 접근 감소

- 접근 속도가 높은 메모리는 자주, 낮은 메모리는 덜 자주 접근하도록 구현된다.

- 필요한 데이터를 상위 계층의 메모리에 옮겨 놓고 사용하면서 낮은 계층의 메모리 접근을 줄인다.

- Locality of reference

- 시간적: 최근에 접근한 데이터에 다시 접근할 가능성이 높다.

- 공간적: 최근에 접근한 데이터의 주변에 위치한 데이터에 다시 접근할 가능성이 높다.

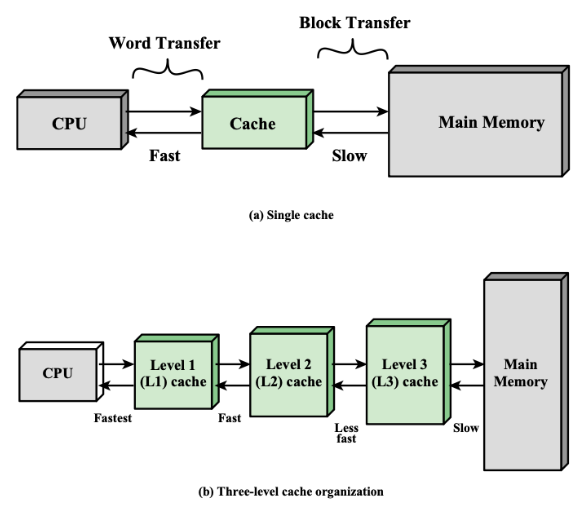

Cache memory

- 메인 메모리의 일부가 블록 단위로 캐시로 옮겨진다.

- Locality of reference 원칙을 구현한 것으로 효율적으로 사용할 수 있다.

- 프로세서는 필요한 데이터를 얻기 위해 캐시 > 메인 메모리> 하드 디스크 순으로 탐색한다.

- 캐시 메모리는 시간 효율성과 복잡성 때문에 OS가 아닌 하드웨어에 의해 관리된다.

- 메인 메모리의 낮은 접근 속도를 해결하기 위해 사용한다.

- 캐시 속도, 메인 메모리 접근 횟수, locality of reference는 시스템 효율성과 관련이 있다.

I/O Techniques

- Programmed I/O -> Interrupt-Driven I/O -> Direct Memory Access 순으로 발전했다.

- Direct Memory Access: 프로세서를 거치지 않고 메모리에 접근하는 방식으로 가장 효율적이다.

- 파일 입출력 같은 대용량 데이터를 처리할 때 사용한다.

- 프로세서는 데이터 이동의 시작과 끝에만 관여하고 그 사이에는 다른 작업을 수행한다.

- I/O 모듈과 메인 메모리 사이에서 데이터가 시스템 버스를 통해 이동하는데, 프로세서가 다른 프로그램을 실행할 때 메인 메모리에서 데이터를 읽어야하는 경우가 있다. 시스템 버스는 단 하나만 존재하기에 이런 경우에는 프로세서의 속도가 느려질 수 있다.

- DMA 모듈은 I/O 모듈의 일부이다.

- I/O 작업 종료를 알리기 위해 인터럽트가 사용된다.

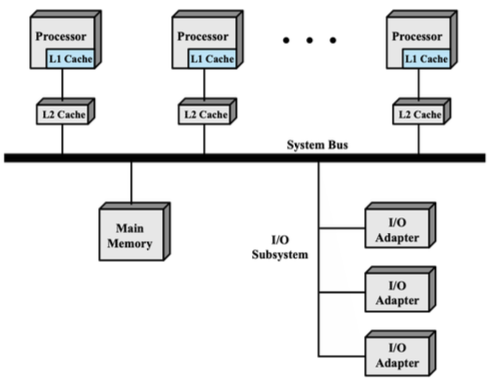

Symmetric Multiprocessors

- 여러 개의 프로세서가 있으면 여러 프로그램이 동시에 실행될 수 있어서 실행 속도가 증가한다.

- 실행 속도는 OS의 영향을 많이 받기 때문에 프로세서 개수에 비례하여 실행 속도가 증가하지는 않는다.

- 하나의 I/O 모듈과 메인 메모리를 여러 프로세서가 공유한다.

- 여러 프로세서가 동시에 동작하는 과정에서 데이터 일관성이 깨지는 문제가 발생할 수 있기 때문에 각 프로세서는 다른 프로세서의 작업이 끝나기를 기다려야 한다.

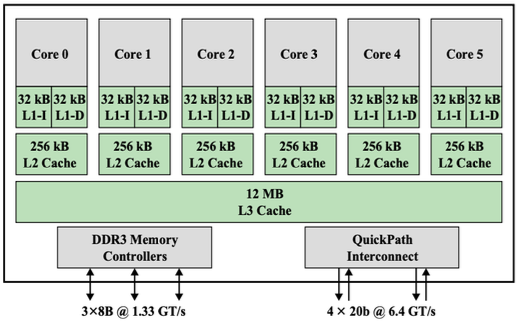

Multicore Computer

잘 보고 있습니다!!