Smart NIC(Network Inteface Card)

정의

network attached acceleration platform. Offloads compute from host processor.

from intel

SmartNIC은 네트워크 인터페이스 카드, 즉 NIC에 가속기가 결합된 네트워크에 통합된 가속 플랫폼이다. SmartNIC은 이러한 가속을 위해 호스트로부터 연산을 오프로딩 해서 대신 수행한다.

이상적인 SmartNIC이 제공해야할 기능은 다음과 같다.

- 전통적인 네트워크 기능 (ex. RDMA)

- 통신 기능과 컴퓨테이션 기능이 하나의 하드웨어로 통합

- 원하는 응용에 특화될 수 있도록 configure, 네트워크 정책이나 응용의 로직이 변경되어도 이를 반영

- 통합된 Software API가 네트워킹 및 가속 기능을 vendor와 상관없이 동일하게 사용

형태

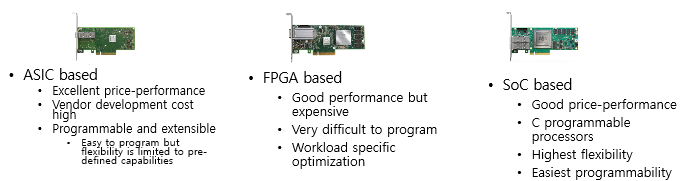

SmartNIC은 크게 세 가지 형태로 구분할 수 있다.

- ASIC 기반

ASIC 기반의 SmartNIC은 CPU 같이 일반적인 목적이 아닌 패킷 처리 같은 특정 목적을 위해 특화된 집적 회로를 사용하는 것으로써, 가장 좋은 가성비를 제공한다. 하지만 벤더의 개발 비용이 높고, 칩셋에서 미리 정의된 기능만 제공할 수 있기 때문에 유연성에 제약이 있다.

- FPGA 기반

사용자가 설정을 바꿔서 원하는 어플리케이션이가 기능을 구현할 수 있는 반도체 장치인 FPGA를 이용하는 방식이다. 워크로드에 맞춰 최적화 할 수 있는 등 유연성이 뛰어나고 성능도 좋지만, 가격이 비싸고 프로그래밍이 매우 어렵다는 단점이 있다.

- SoC 기반

System on chip의 약자로, CPU, 메모리, I/O 포트 등의 여러 컴포넌트를 하나의 집적 회로로 통합한 것을 말한다. 이를 이용한 SmartNIC은 좋은 가성비를 제공하며, C 언어 등으로 프로그래밍 할 수 있기 때문에 유연성이 높고, 프로그래밍이 용이하다.

가성비는 ASIC, 프로그래밍 용이성 및 유연성은 SoC 기반의 SmartNIC이 가장 좋다.

내부 구조

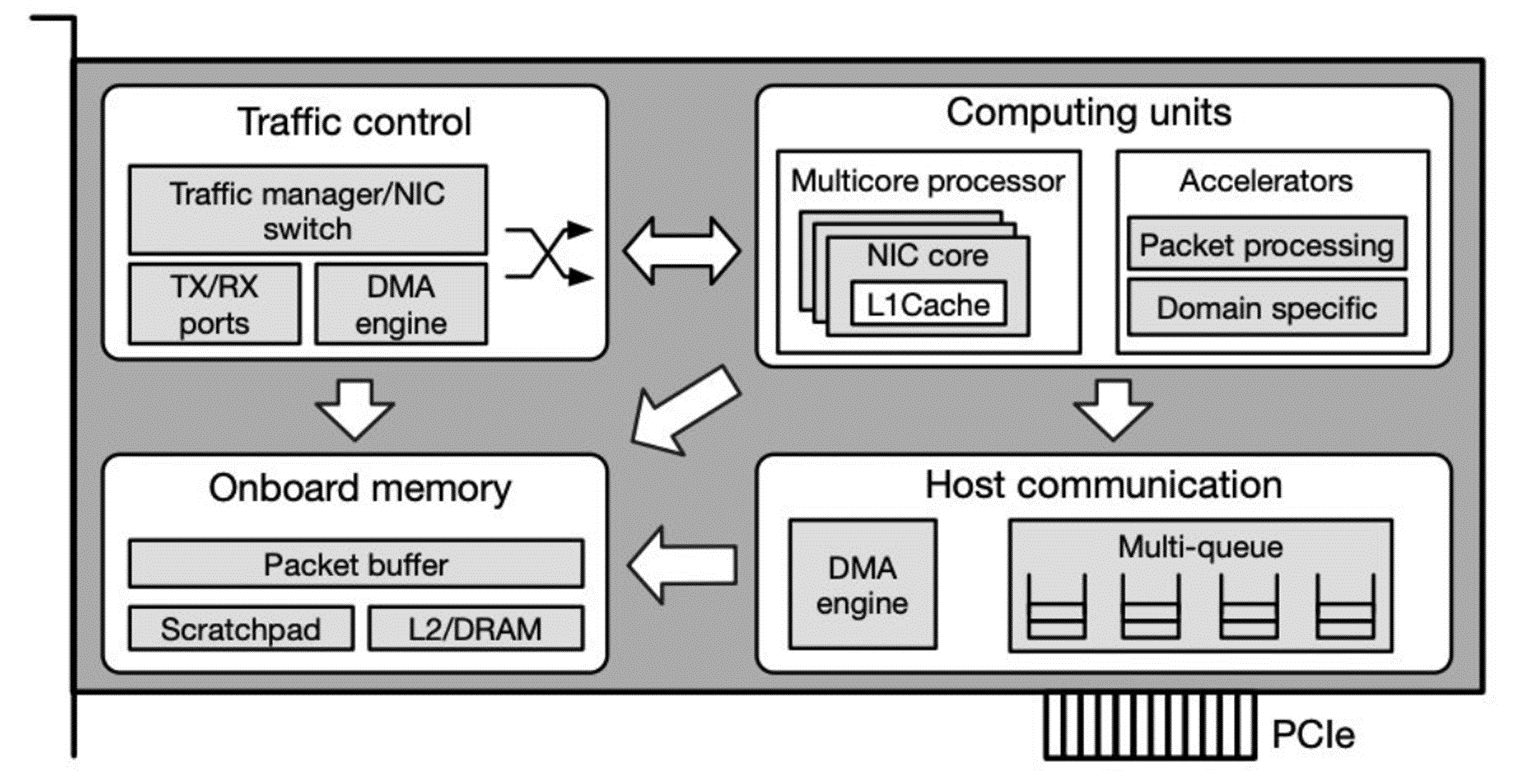

SoC 기반의 SmartNIC 구조를 살펴보겠다. 멀티 코어 SoC 기반 SmartNIC은 네 개의 주된 요소로 구성되어 있다.

-

Computing Unit: general-purpose ARM 혹은 MIPS 멀티코어 프로세서와 DPI나 패킷 버퍼 관리 등과 같은 기능을 수행하는 패킷 처리 가속기, 그 밖에 암호화/복호화, 해싱, 패턴 매칭, 압축과 같은 특정 기능을 위한 가속기 등을 포함한다.

-

onboard memory: 패킷 버퍼, 연산, 데이터 등의 임시적 저장을 위해 사용되는 Scratchpad 메모리, L2 캐시/DRAM 등을 포함한다.

-

traffic control module: TR/TX ㅍ트와 패킷 버퍼 간의 패킷을 이동시키는 역할을 하고, NIC core로 패킷을 전달해주는 트래픽 manager 또는 NIC 스위치를 포함한다.

-

DMA engine: PCIe 인터페이스를 통해 호스트와 통신하기 위한 DMA 엔진