1. Porting to Black & White

At previous posts, I have dealt with B1 and JY server. As JY server had 10900k, which did not support ACS, we had to think about the test scenario.

We had to:

1) Satisfy

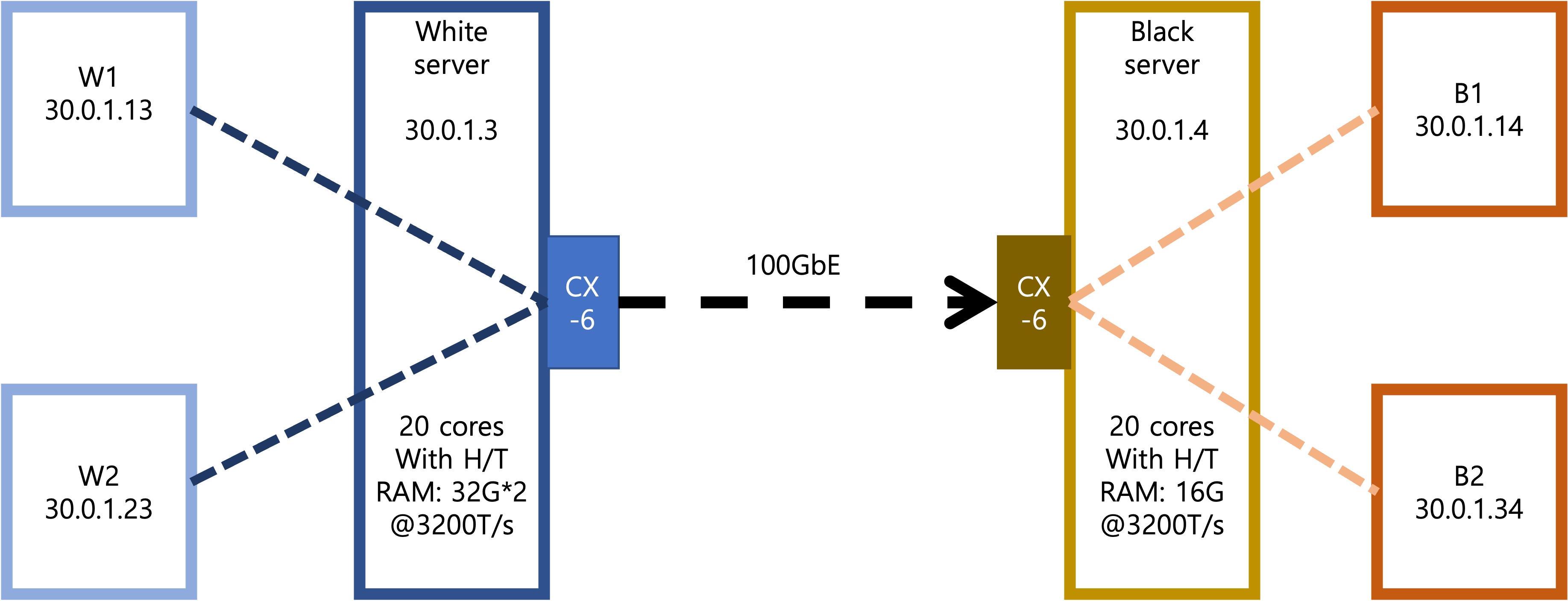

Thus the final result of our test scenario looks as:

2. RSS Test

3. Baseline Test Prepare

To find the best fit setting, I had to consider:

1) Memory Allocation - memory isolation is garaunteed, yet total should not reach max

2) CPU Allocation - should isolate CPU usage as much as possible even with the host

3) Performance degration - should show atleast near-max performance without contention

'#' of hugepage needed showed similar to # of CPUs.

Thus, needed to find out "performance per # of CPU" -> # of memory

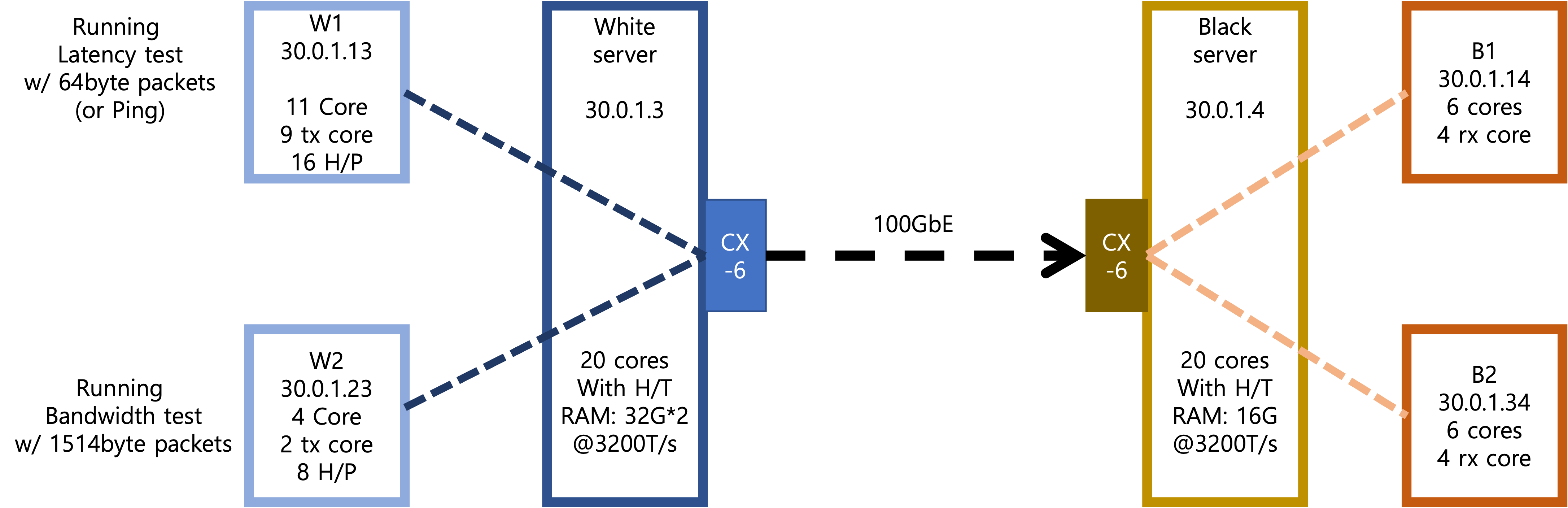

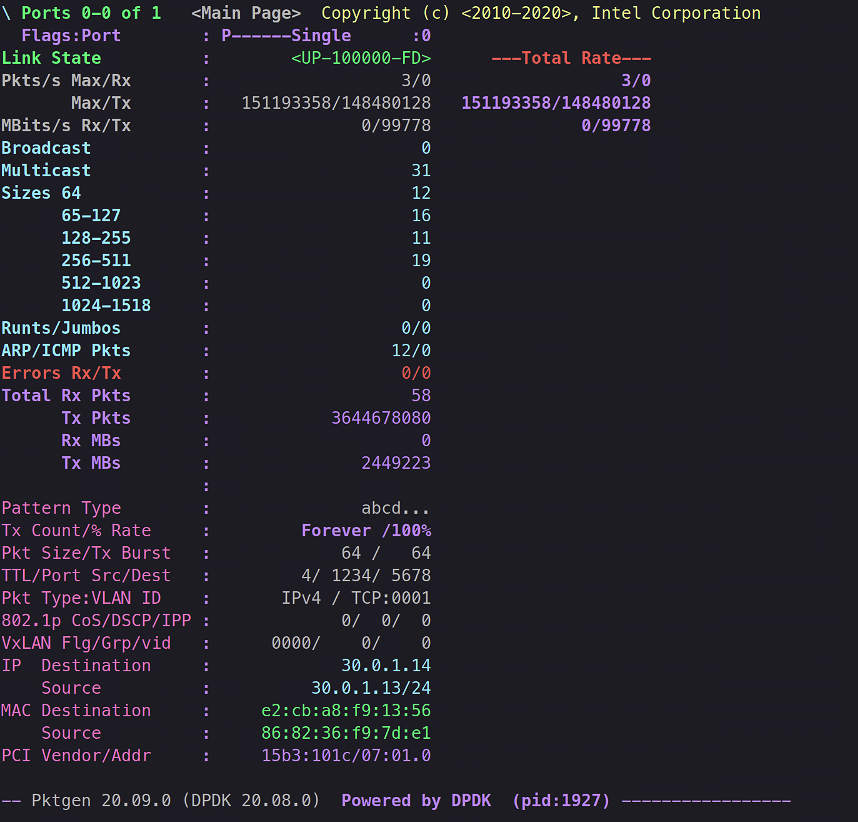

W1-> B1 (9tx cores)

W2 -> B2 (4 tx cores)

4. Test Result - Latency at Baseline

Weird thing 1) Latency measuring side

Measuring is done at Reciever side..?

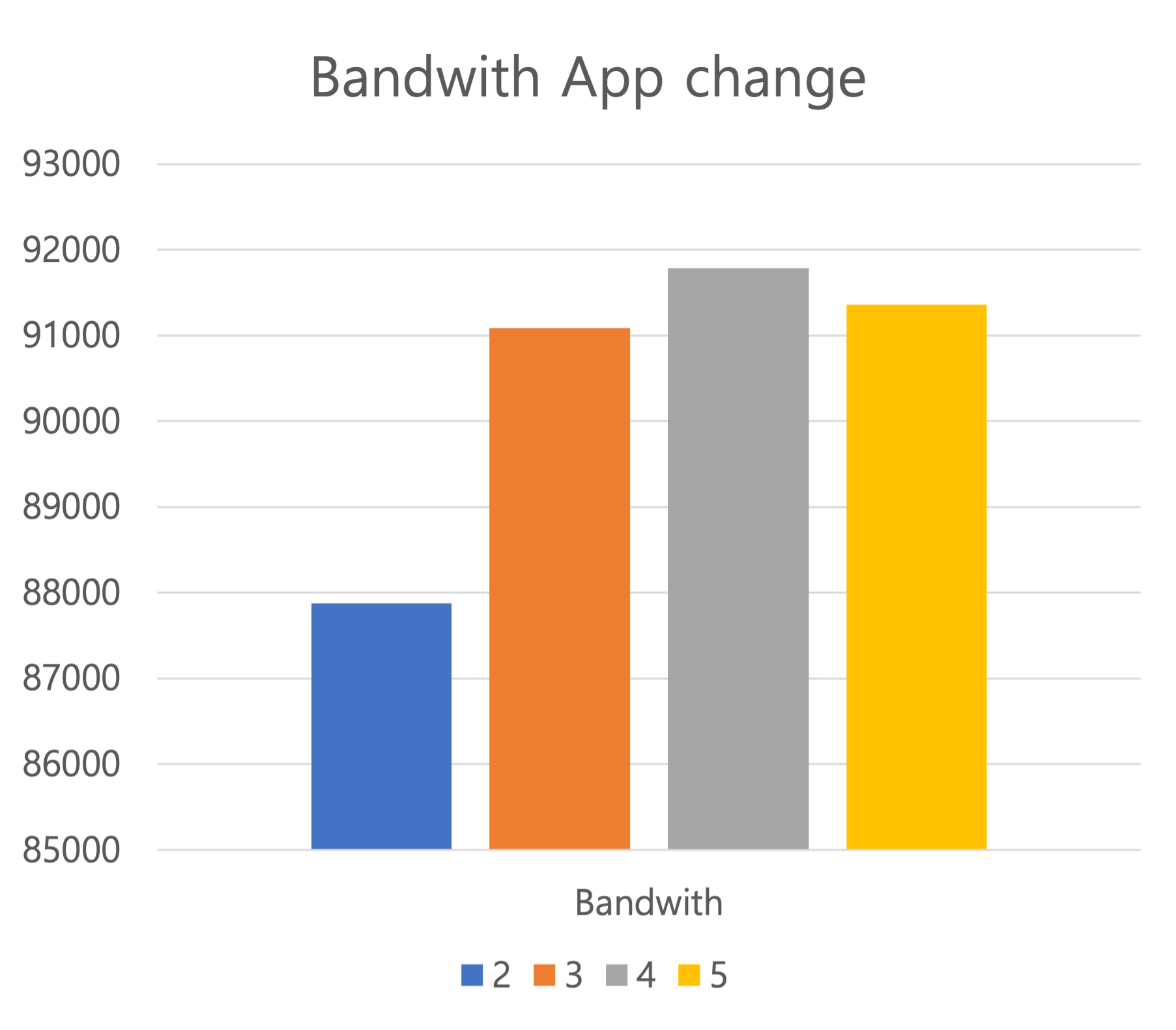

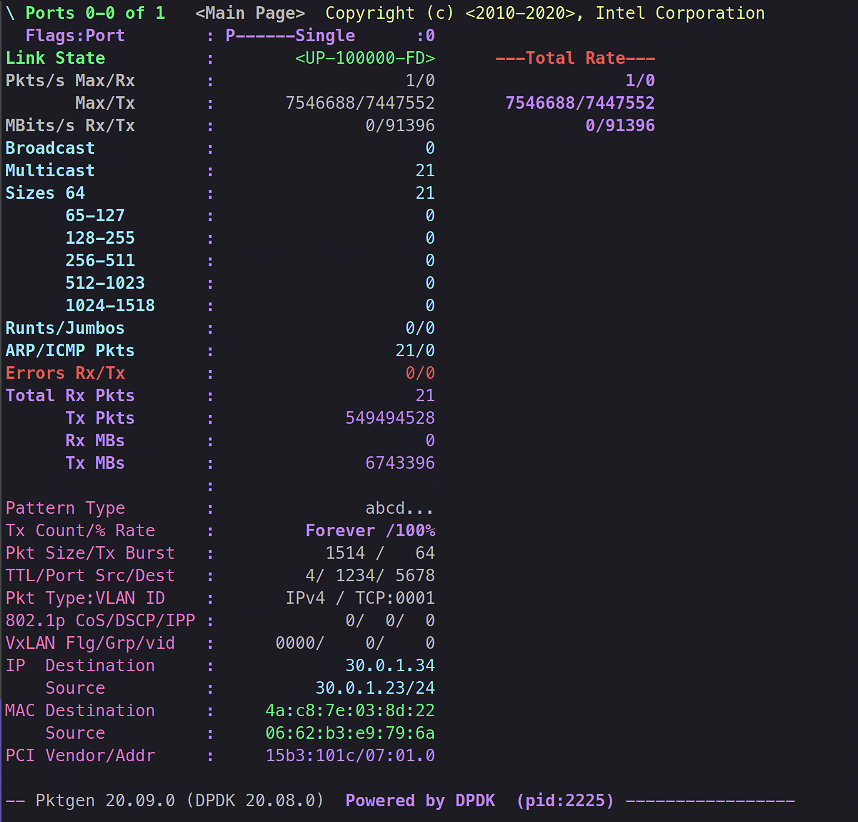

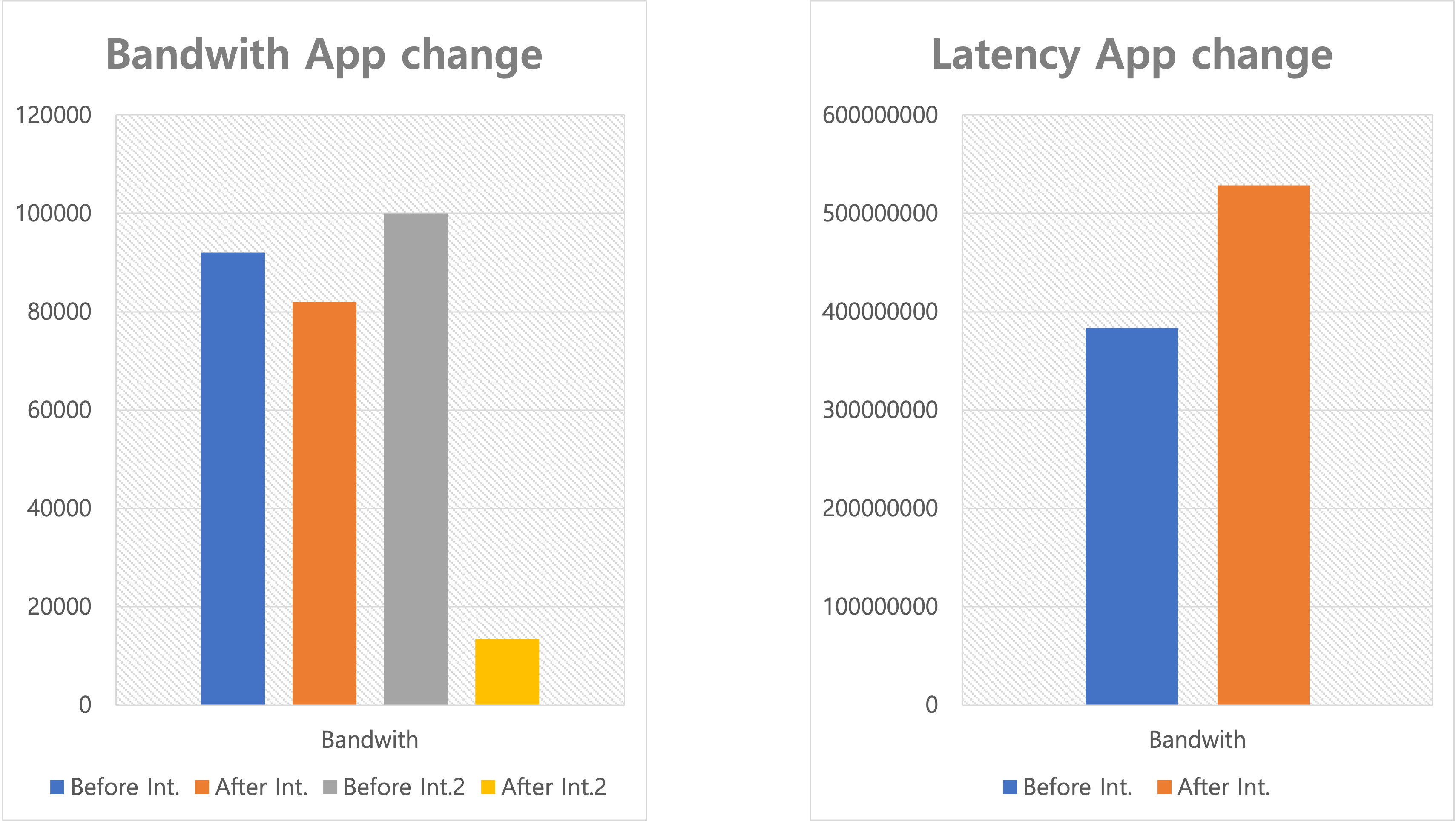

Weird thing 2) Bandwith

=> Bandwith degrades too much?

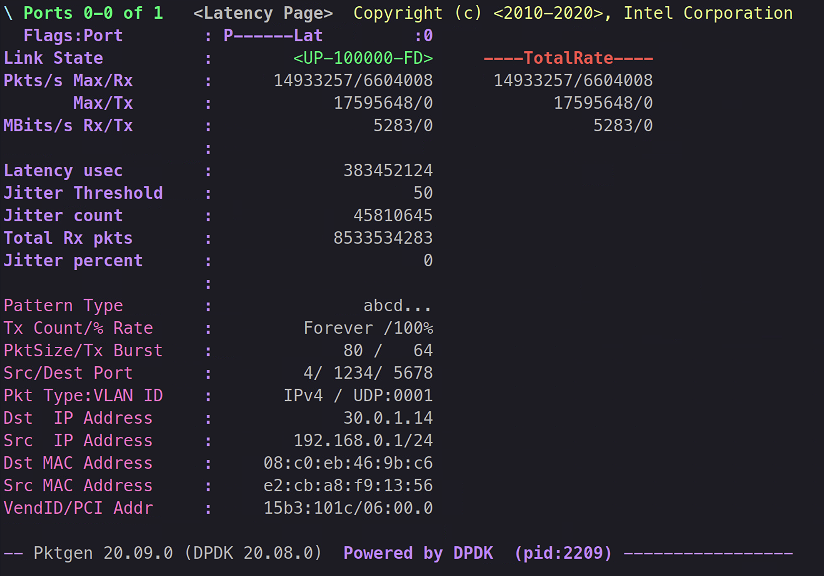

Weird thing 3) Latency

usec is 10^-6sec, which means latency is 383.4 sec.

말이 되나 이게..?

Result

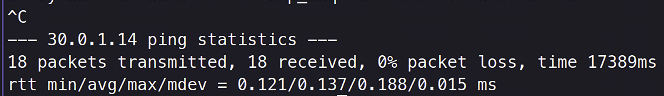

4.1 Test Result - Latency with ping

Before

After

Slight change?

5. Test Result - Latency at QoS

TBD

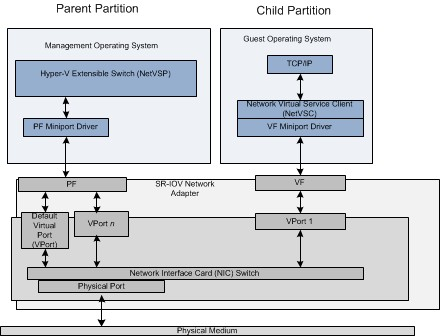

6. PF and VF

여기가 MS쪽 사진이라서 miniport driver라고 되어 있는데 이건 그냥 개념적인 차원에서 전체 드라이버가 아닌 특정 부분만 수행하는 드라이버라는 의미에서 이렇게 쓴 것 같고, 멜라녹스 쪽에서는 완전히 구분짓는 것 같진 않음(문서에도 레지스트리 관련된 내용만 있고, 드라이버 코드에는 미니포트 관련된 부분이 보이진 않음)

그래서 mlx5 기준으로 동작 자체는 구분되는데 실질적으로 드라이버가 크게 구분되지는 않고, 동일하게 mlx5 드라이버가 올라간 채로 사진처럼 동작하게 됨.

여기서 VSC가 pci쪽 용어인 것 같은데 자세히는 모르겠고, mlx5도 vf쪽에만 저렇게 별도로 뭔가 할당되는걸 봐선 PCI쪽에서 뭔가 제너릭한게 있지 않나 싶음

/lib/pci_vsc.c

mlx5에서는 sriov.c에서 sriov를 켜면 vf들을 설정해주고 하는 걸 하고, 그 과정에서 sriov_sysfs.c에서 추가적으로 관련된 내용들을 커널에 기록해서 실질적으로 처리해주는 걸로 보임

그리고 그게 mlx5가 MS에서 소개하는 페이지들에서 설명하는거랑 완전히 동일한지는 조금 더 봐야 하겠지만, 아무튼 기본적으로 pf가 있는 호스트 쪽에서 (당연하지만)SR-IOV를 활성화한다던지 하는 역할을 수행하고, 이 pf에서 vf들을 관리하게 됨

그 관리라고 하는건 대단한건 아니고, 단순히 VF가 새로 등록될 때 이걸 PF에 요청하면 그게 잘 올라갔는지 등에 대해서 처리함.