레지스터(register)

- 외부에서 들어오는 여러 비트 데이터를 저장하거나 이동하기 위해 사용 --> 플리플롭은 한 비트의 값을 저장 but 레지스터 플리플롭을 이용해 여러 비트를 저장(ff->register-->counter)

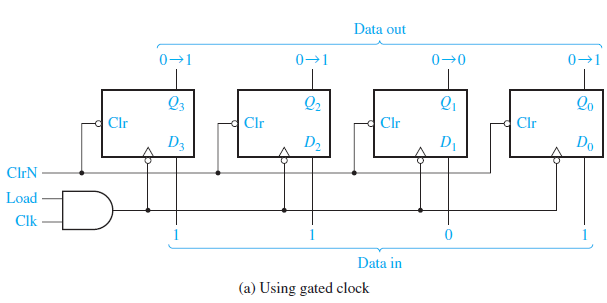

- 위 그림은 레지스터 회로를 나타낸 것임, 회로말고 레지스터 자체로 나타낼 수 있음

- 플리플롭 여러개를 조합하여 구성

- 여러 비트 저장 가능

- 우선순위: clear > clock > load(clear는 clock에 상관없는 비동기 신호임)

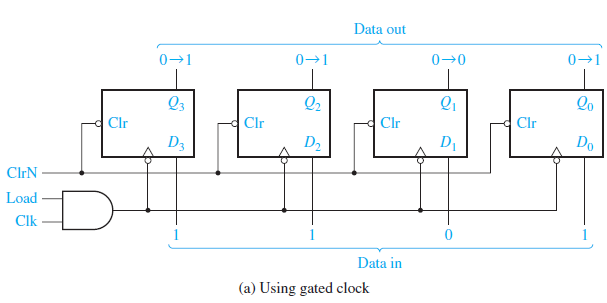

shift register(동기)

- 매 클럭마다 한칸씩 값이 이동(우측/좌측)

- 4-bit bidirectional shift register

- 00 --> hold

- 01 --> right

- 10 --> left

- 11 --> load

counter

- 매 클락마다 값이 증가

- 요소

- reset: 0부터 시작

- load: 새로운 값으로 업데이트

- tc: 최고로 많은 값을 카운트 했음을 외부에 알려줌

- cnten(Count enable): 1인 경우에만 count가 증가 할 수 있음, 0인 경우는 count 증가 못함

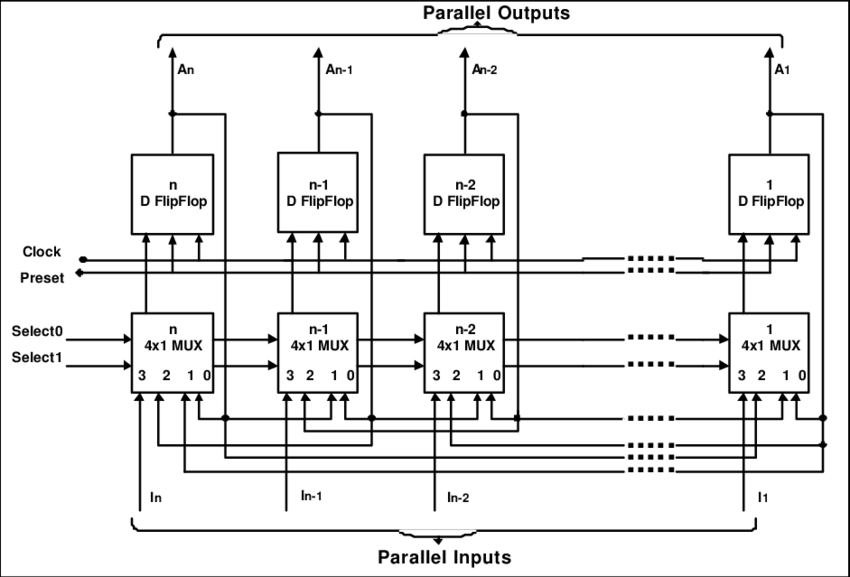

ripple counter(비동기 카운터, asynchronous counter)

-

신호가 저레벨에서 고레벨 플리플롭으로 전파됨

-

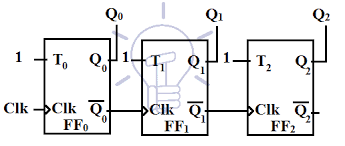

t counter --> 가장 만들기 쉬움, 가장 기본이 되는 ripple counter임

- 낮은 자리의 비트가 1-->0으로 줄어들 때, 다음 자리의 비트가 0-->1로 변화(000 ~ 111까지 적어보면 알 수 있음 --> 귀납적으로 저런 규칙을 발견한 것!)

- postive ff이므로 q'값을 다음 ff의 clock 값으로 넣어줌

-

ripple counter 단점

- propagation delay

- 클럭 주기가 짧은 경우 더 치명적(같은 딜레이가 주기에 비해 큰 부분을 차지함)

- 비트가 큰 경우 더 치명적

- 이를 보완한 것이 동기 카운터임 --> 모두 같은 clock을 사용

- propagation delay

synchronous counter(동기 카운터)

- 비동기 카운터와 달리 모든 플리플롭이 동시 변화(모두 같은 clock을 사용)

- 낮은 비트의 비트가 모두 1인 경우 --> 다음 값이 토글됨

- ripple은 클락이 1-->0인 경우 즉각적으로 0-->1로 변화 VS 동기는 낮은 비트가 모두 1인 경우 다음 클락에서 0으로 변화(값이 변하는 것이 클락의 변화와 상태의 차이가 있음!) ==> ripple은 q(or q'-결과값)값이 Counter에 연결되어 있으므로 즉시 바뀌고, Synchronous는 Clock 값이 따로 있으므로 q(or q')은 다음 값에 영향을 줌!

- t는 이전 ff의 바뀐 값이 바로 적용되는 것이 아니라, 이전 clock의 이전 ff의 t값이 적용됨

- sequential p20

- 74ls163a(sequential p29)

- 우선순위: reset(SR) > load(PE) > enable(CEP * CET=1) > count up

- disenalbe의 경우 hold임

- 기본적으로 다 synchronous이므로 clock이 엣지인 경우만 작동됨!(tc빼고)

- tc는 cobinational logic 값이므로 asynchronous임

- 우선순위: reset(SR) > load(PE) > enable(CEP * CET=1) > count up

reset

- ripple의 경우 다음 값을 인지 후 그 값을 clear를 통해 0로 만들어줌 --> 10-mod: 1010까지

- 동기 카운터의 경우 다음 값을 로드하기 위하여 해당 값을 받고 바로 load를 취함 --> 1001까지