플립플롭과 메모리 동작

메모리의 동작도 반가산기와 전가산기때 처럼 이해하기 위해 알아야할 사항이 많다 우선 플립플롭이 어떤식으로 생기거 어떻게 변하는지 부터 설명해야 할 것 같다.

플립플롭(데이터를 저장 할 수 있는 논리회로)이란?

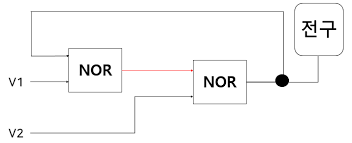

플립플롭은 데이털를 저장 할 수 있는 논리회로로서 0과 1을 위의 그림처럼 전구에 빗대어 말하자며 기존에 누군가 전구를 켠적이 있는지 없는지 알 수 있도록 설계된 회로이다. 그림과 같이 기본적으로 NOR게이트 사이의 전선에 전류가 흐르는 상태로 만약 v1에 전류를 흘려본다면 전구에는 불이 들어온다 하지만 전류를 다시 차단한다 하려도 전구의 불은 꺼지지 않으며 이는 기존에 전구를 켰다는 사실을 기억 할 수 있다는 것이다. 여기서 v2에 전류를 연결하면 가장 처음 상태로 다시 돌아간다

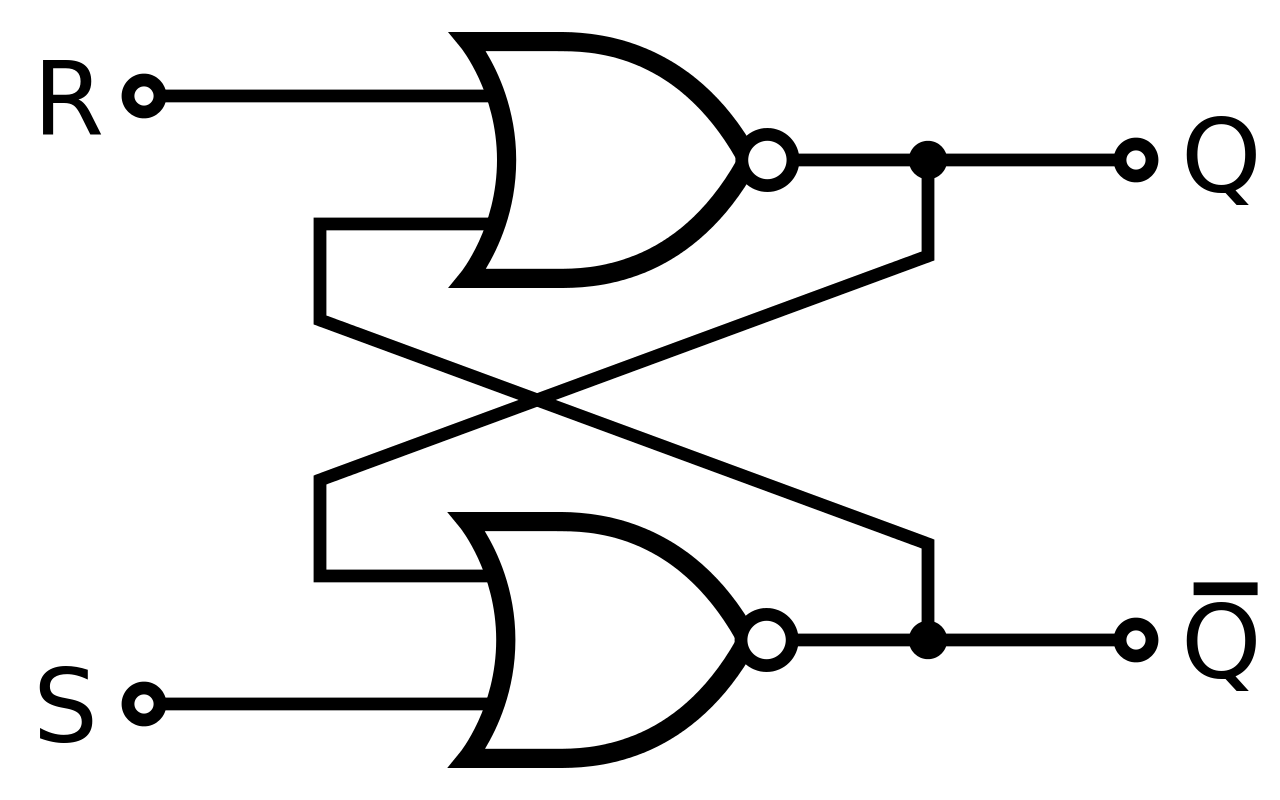

RS(Reset,Set)플립플롭에 대해

RS 플리플롭은 위에서 보았던 전구를 좀 다르게 표현한 것일뿐이다

위의 그림과 같이 표현된 논리회로를 RS 플립플롭이라 하고 S에 전류를 흐르게 한다면 Q에는 데이터가 1비트의 이진수 데이터가 기억되고 R에 전류를 흐르게 한다면 데이터를 Q의 데이터는 0 다른 데이터는 1이 된다. 여기서 R과 S에 동시에 전류가 흐른다면 기억와 초기화가 동시에 되는 일이 발생하므로 이 점에 주의해야한다.

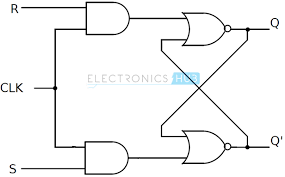

Level-triggered flip-flop(레벨 트리거드 플립 플롭)

이 플리플롭은 CLK(hold that Bit)이 추가된 형태이다 이 형태의 특징은 R이나 S가 1이 되었다 하더라도 CLK가 1이 되어야 AND 게이트를 지나 값을 수정 할 수 있다는 것이다.

(CLK 는 CPU의 클럭이다)

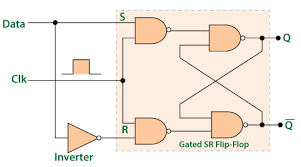

D-type flip flop

이 D-type flip flop은 위의 level-triggered flip-flop에서 R과 S의 부분을 하나로 통합시켜 기존의 R과 S의 동시에 켜지면 생길 수 있는 문제를 해결 할 수 있다. 또한 둘다 0일때도 생길 수 있는 문제에 대해서도 해결 할 수 있게되었다.

다음은 이걸 토대로 메모리의 작동원리에 대해 포스팅하겠습니다.