PC 3대장

CPU,Memory,Disk

CPU

- 모든 디바이스 관장

- n개의 register로 구성

- 코어의 개수가 늘어날 때마다 register의 n개의 set이 늘어난다.

n x state

- 코어의 개수가 늘어날 때마다 register의 n개의 set이 늘어난다.

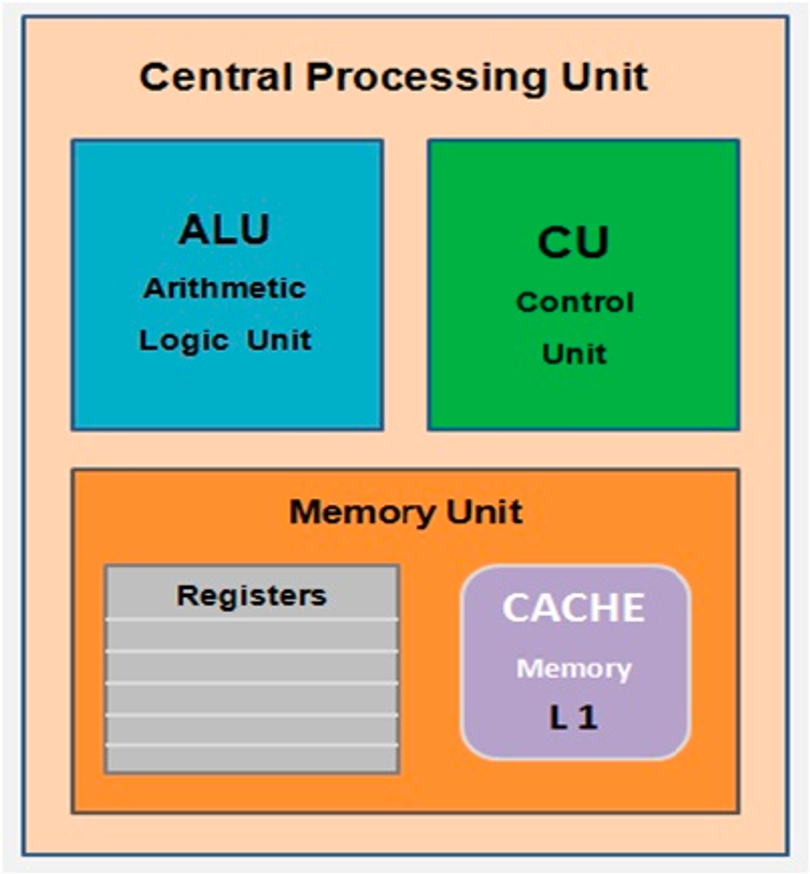

CU(Control Unit),ALU(산술/논리 연산),register,cache로 구성

CPU가 싱글코어에서 멀티코어로 바뀐 이유

무어의 법칙이 말해주듯 코어 성능(클럭 수)은 계속 고도화 잘 되고 있음- 무어의 법칙 : 2년마다 프로세스 성능 2배 증가

- 발열문제

- 코어 성능 향상에는 본질적인 한계가 있으므로 멀티코어로 진화

멀티코어 : 멀티한 상태(state == register)를 가진다.

CPU 생김새

CU

- real brain

- 명령 내리는 역할

ALU

- 산술 / 논리 연산 담당

register

- cpu 명령어 처리하기 위해 필요한 여러 데이터를 용도에 맞게 저장하고 있는 도우미

- 범용 레지스터 : EAX, ECX, EDX ...

- 전용(특수) 레지스터 : PC (프로그램 카운터) ...

cache

- CPU 성능 향상을 위해 고안된 지름길

- 빈번한, 가장 최근의

캐싱한다- 음료를 사려고 1km 떨어진 편의점(메모리)에서 고를 것인지, 10m 떨어진 자판기(캐시)에서 고를 것인지

- 자판기에 원하는 음료가 있다면?

cache hit - 원하는 것이 없어 편의점까지 가는 것은?

cache miss

- 자판기에 원하는 음료가 있다면?

cache coherence

- 캐시 일관성

- 공유 메모리 시스템에서 각 프로레서가 가진 로컬 캐시 간의 일관성

프로그래머와 CPU의 통신 방법

- CPU : 바이너리 원툴 == 기계어

- 사람은 기계어 사용 못함 -> 유사 기계어인 어셈블리어 사용

- 어셈블리어는 CPU 아키텍처에 따라 문법이 다름

- 연산자는 LOAD, STORE, JMP와 같은 원초적 명령어로 구성

- 피연산자는 메모리 주소, 레지스터, 즉시 값 중 하나만 사용 가능

- 어셈블리어는 개발자들이 쓰기에도 어려움

프로그래밍 언어 탄생

- c, c++, java ...

- 각 언어에 있는 컴파일러가 사람이 작성한 코드를 기계어로 번역

- 컴파일러 == 통역

즉, CPU와 프로그래머는 프로그래밍 언어로 통신한다!

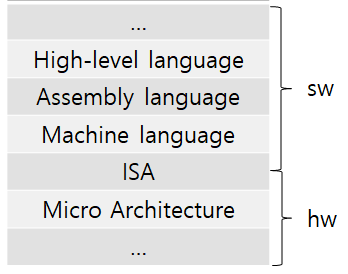

ISA

- Instruction Set Architecture

- 소프트웨어(시스템 소프트웨어)와 하드웨어 사이의 약속(인터페이스)

- 개발자들은 보통 high-level language로 코드를 짠다.

하지만 컴퓨터가 이를 이해하기 위해서는 어셈블러(high-level language → assembly language)와 컴파일러(assembly languabe → machine language)를 거쳐 low-level lanaguage로 번역되어야 한다.

이렇게 low-level language로 번역된 후에는 hw에게 명령을 내려줘야 하는데, 이 때 sw와 hw 사이를 연결해주는 것이 ISA이다.

CISC

- 복잡하고 기능이 많은 명령어로 구성

- 범용 컴퓨터(general-purpose computer)의 CPU로 많이 사용

RISC

- 요즘 대세

- 적은 수의 명령어들(사용 빈도가 높은 20%의 명령어들)로 구성

- 간단

[References]

명령어 수행 방법

- 프로그래밍 언어에 작성된 코드는 라인마다 기계어 연산으로 치환

- 명령어 인출

CU가 수행할 명령어 정보 가져옴 - 명령어 해독

opcode라고 하는 명령어 코드를 인출하고,

opcode의 성격에 맞게 레지스터 준비 - 실행

해독된 명령어 수행

산술 논리 관련 연산이라면 ALU가 실행 - 반영

명령어 수행 한 사이클 끝